# 4.7V to 18V Input, 5A Synchronous Buck Regulators with AOT Control

### **Features**

- Wide VIN Range: 4.7V to 18V

- Maximum Continuous Output Current: 5A

- Vout = 1.8V

- Different fixed options are available for predefined output voltage by the factory.

- Integrated High / Low-Side FETs (65mΩ / 35mΩ)

- Advanced Adaptive On-Time Control

- Fast Transient Response

- · Open Drain Power Good Indicator

- ±0.5% Feedback Voltage Reference

- Zero Shutdown Supply Current

- 50µA Non-Switching Operating Quiescent Current

- 80µA No Load Operating Quiescent Current

- High Efficiency in Light Load and Heavy Load.

- Factory 300kHz, 500kHz, 800kHz, and 1MHz

Switching Frequency options available by request

- Internal Soft-Start

- Factory Forced CCM (FCCM) or automatic CCM/PFM (Auto-Skip) Options

- Active discharge Mode option

- Ultrasonic Mode option to Eliminate Audio Noise

- Built-in Cycle-by-Cycle Current Limit, Short Circuit Protection, Input UVLO, Output Under-Voltage Protection, Output Over-Voltage Protection, and Thermal Shutdown Protection

- 11-Pin UQFN (2.2mm x 2.5mm) Package

# **Applications**

- CPU, GPU, AP, DSP, FPGA, VIO, VSYS

- HDD, LPDDR3, LPDDR4 Memory Power

- Tablets, Netbooks, Ultra-Books, Mobile Internet Devices, IoT, and Server.

- DSC, Drones, Gaming Consoles, TV Set Box

## **Description**

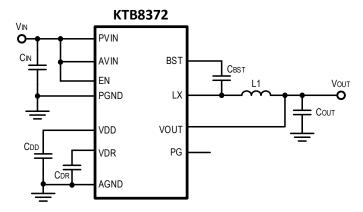

KTB8372 is 5A, 18V synchronous buck regulators with integrated high-side and low-side power FETs. The device operates over a wide input voltage range to support a variety of applications with input voltage from regulated 5V and 12V power rails and multicell batteries. The fix options for output voltage can be predefined and trimmed by the factory.

KTB8372 employs Kinetics' proprietary advanced adaptive on-time (AOT) control for fast transient response and high output voltage accuracy. This control technique eliminates external loop compensation network and allows the use of ceramic output capacitors without ripple-generating circuitry. These features enable very small total solution size and make KTB8372 easy to use.

The device features an internal soft-start function to limit inrush current during start-up. The device has comprehensive built-in protection features including input voltage UVLO, high-side cycle-by-cycle peak current limit, low-side valley current limit, reverse current protection, short-circuit protection, output overvoltage protection, and thermal shutdown.

KTB8372 are available in RoHS and Green compliant 11-Pin UQFN (2.2mm x 2.5mm) package.

# **Typical Application Schematic**

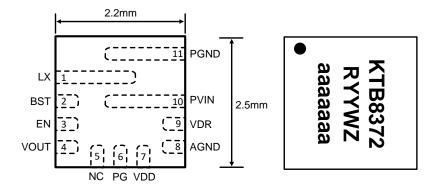

# **Pinout Diagram**

### **Top Mark**

UQFN-11 Package

(2.20mm x 2.50mm x 0.55mm)

RY = Device ID Code, YW = Date Code, Z = Serial Number aaaaaaa = Assembly Lot Tracking Number

# **Pin Descriptions**

| Pin Name |      | Function                                                                                                                                   |  |  |  |  |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1        | LX   | Inductor connection for buck regulator.                                                                                                    |  |  |  |  |

| 2        | BST  | Boost capacitor for charge pump gate driver.                                                                                               |  |  |  |  |

| 3        | EN   | Chip enable logic input.                                                                                                                   |  |  |  |  |

| 4        | VOUT | Output voltage sense input.                                                                                                                |  |  |  |  |

| 5        | NC   | NC Pin, must be tied to AGND.                                                                                                              |  |  |  |  |

|          |      | Open-drain Power Good Indicator Output. Connect a pull-up resistor                                                                         |  |  |  |  |

| 6        | PG   | between PG pin and VDD pin, a resistor ranges from $10k\Omega$ to $100k\Omega$ is                                                          |  |  |  |  |

|          |      | recommended. This pin is pulled to ground when the output voltage is outside of its specified threshold. If not used, tie to AGND or PGND. |  |  |  |  |

| 7        | VDD  | Analog circuit bias voltage.                                                                                                               |  |  |  |  |

| 8        | AGND | Analog ground for analog circuit.                                                                                                          |  |  |  |  |

| 9        | VDR  | Power stage driver voltage.                                                                                                                |  |  |  |  |

| 10       | PVIN | Input Voltage Power and Sense Pins for buck regulator.                                                                                     |  |  |  |  |

| 10       |      | Connect to a power rail ranges from 4.7V to 18V.                                                                                           |  |  |  |  |

| 11       | PGND | Power ground for buck regulator.                                                                                                           |  |  |  |  |

## **Ordering Information**

|                          | _                    | Default Settings <sup>3</sup> |        |                           |                      |                    |         |

|--------------------------|----------------------|-------------------------------|--------|---------------------------|----------------------|--------------------|---------|

| Part Number <sup>1</sup> | Marking <sup>2</sup> | Vout                          | Fsw    | FCCM or Auto-Skip<br>Mode | Active<br>Discharged | Ultrasonic<br>Mode | Package |

| KTB8372CEUFA-5C-TA       | RYYWZ                | 1.8V                          | 500kHz | Auto-Skip                 | Disabled             | Disabled           | UQFN-11 |

# Absolute Maximum Ratings<sup>4</sup>

(T<sub>A</sub> = 25°C unless otherwise noted)

| Descripti                            | ion                                      | Value               | Units |

|--------------------------------------|------------------------------------------|---------------------|-------|

| PVIN to F                            | PGND                                     | -0.3 to 19          | V     |

| PGND to                              | AGND                                     | -0.3 to 0.3         | V     |

| LX to PG                             | ND                                       | -0.3 to (PVIN +0.3) | V     |

| BST to LX                            |                                          | -0.3 to 5.5         | V     |

| VOUT, VDD, VDR, EN, and PG to AGND   |                                          | -0.3 to 5.5         | V     |

| LX                                   | Continuous Current                       | 7                   | Arms  |

| LA                                   | Peak Current (2.5ms maximum)             | 10                  | Apeak |

| Operating Junction Temperature Range |                                          | -40 to 150          | °C    |

| Storage Temperature Range            |                                          | -55 to 150          | °C    |

| Maximum                              | Soldering Temperature (at leads, 10 sec) | 260                 | °C    |

# **ESD Ratings**<sup>5</sup>

| Symbol                  | Description                                                              | Value | Units |

|-------------------------|--------------------------------------------------------------------------|-------|-------|

| V (ESD)                 | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins             | ±2000 | \/    |

| Electrostatic Discharge | Charged device model (CDM), per JEDEC specification JESD22C101, all pins | ±500  | V     |

# Thermal Capabilities<sup>6</sup>

| Symbol         | Description                                        | Value | Units |

|----------------|----------------------------------------------------|-------|-------|

| ΘJA            | Thermal Resistance – Junction to Ambient           | 59.6  | °C/W  |

| P <sub>D</sub> | Maximum Power Dissipation at T <sub>A</sub> = 25°C | 1.67  | W     |

| ΔΡD/ΔΤ         | Derating Factor Above T <sub>A</sub> = 25°C        | -16.7 | mW/°C |

December 2023 – Revision 4a Page 3 of 13 Kinetic Confidential

<sup>1.</sup> For part numbers in italics or alternative default combinations, please contact your local sales representative.

<sup>2.</sup> RY = Device ID Code, YW = Date Code, Z = Serial Number. aaaaaaa = Assembly Lot Tracking Number.

<sup>3.</sup> Contact a Kinetic Technologies representative regarding versions with other default settings.

<sup>4.</sup> Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

ESD Ratings conform to JEDEC industry standards. Some pins may have higher performance. Ratings apply with chip enabled, disabled, or unpowered, unless otherwise noted.

<sup>6.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

# Electrical Characteristics<sup>7</sup>

Unless otherwise noted, Typ values are specified at  $T_J = +25^{\circ}C$  with  $V_{IN} = 12V$ . The Min and Max specs are applied over the full operation temperature range of  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  and  $V_{IN} = 4.7V$  to 18V.

| Symbol               | Description                                       | Conditions                                                             | Min  | Тур  | Max | Units |

|----------------------|---------------------------------------------------|------------------------------------------------------------------------|------|------|-----|-------|

|                      | pecifications                                     |                                                                        |      |      |     |       |

| $PV_{IN}$            | Input Supply Operating Range                      |                                                                        | 4.7  |      | 18  | V     |

| Vuvlo                | Under Voltage Leekout Threshold                   | V <sub>IN</sub> rising                                                 | 3.35 | 4.25 | 4.7 | V     |

|                      | Under-Voltage Lockout Threshold                   | Hysteresis                                                             |      | 500  |     | mV    |

|                      |                                                   | EN = High, V <sub>IN</sub> = 12V, Non-Switching                        |      | 50   |     | μΑ    |

| IIN                  | VIN Supply Current                                | EN = High, V <sub>IN</sub> = 12V, Auto-Skip                            |      | 80   |     | μΑ    |

|                      |                                                   | EN = High, V <sub>IN</sub> = 12V, Forced-PWM                           |      | 10   |     | mΑ    |

| I <sub>SHDN</sub>    | Shutdown Supply Current                           | $EN = Low, T_A = 25^{\circ}C$                                          |      | 0.01 | 1   | μΑ    |

| Logic Pir            | n Specifications (EN, PG)                         |                                                                        |      |      |     |       |

| V <sub>IH</sub>      | Input Logic High (EN)                             |                                                                        | 3.8  |      |     | V     |

| VIL                  | Input Logic Low (EN)                              |                                                                        |      |      | 0.4 | V     |

| I <sub>I_LK</sub>    | Input Logic Leakage (EN)                          | T <sub>A</sub> = 25°C, V <sub>EN</sub> = 5V                            |      | 0.01 | 1   | μA    |

| Vol                  | Output Logic Low (PG)                             | Io_sink = 100μA                                                        |      |      | 0.4 | V     |

| lo_lk                | Output Logic Leakage (PG)                         | T <sub>A</sub> = 25°C, V <sub>O</sub> = 5.5V                           |      | 1.5  | 3.8 | μA    |

|                      | Shutdown Specifications                           | , -                                                                    |      | ı    |     |       |

|                      | •                                                 | T <sub>J</sub> rising                                                  |      | 150  |     | °C    |

| $T_{J\_SHDN}$        | IC Junction Thermal Shutdown                      | Hysteresis                                                             |      | 20   |     | °C    |

| Buck Red             | gulator Specifications                            | , , , , , , , , , , , , , , , , , , , ,                                |      |      | I   |       |

|                      | Output Voltage Setting Range                      | Factory Programmable Options                                           | 0.64 |      | 5.5 | V     |

| Vout                 |                                                   | Output Voltage Step                                                    |      | 40   |     | mV    |

| Vour_acc             | Output Voltage DC Accuracy                        | T <sub>A</sub> = 25°C, FCCM                                            | -0.7 |      | 0.7 | %     |

| I <sub>OUT_max</sub> | Maximum Continuous Output Current                 | .,, == 0,: 00                                                          | 5    |      |     | Α     |

|                      | High-Side Switch Peak-Current Limiting            |                                                                        | 6.4  | 8    | 9.6 | Α     |

| I <sub>peak</sub>    | Threshold                                         |                                                                        | 0.4  | 0    | 9.6 | А     |

| I <sub>valley</sub>  | Low-Side Switch Valley-Current Limiting Threshold |                                                                        | 6    | 7.5  | 9   | Α     |

| I <sub>rev</sub>     | Low-Side Reverse Current Limiting Threshold       | FCCM Mode                                                              |      | -3   |     | Α     |

| I <sub>zcd</sub>     | Zero-Crossing-Detection Threshold                 | Auto-Skip Mode                                                         |      | 0    |     | mA    |

| R <sub>dson_h</sub>  | High-Side Switch On-Resistance                    |                                                                        |      | 60   | 75  | mΩ    |

| R <sub>dson_I</sub>  | Low-Side Switch On-Resistance                     |                                                                        |      | 30   | 40  | mΩ    |

| R <sub>LX_DIS</sub>  | LX Active Discharge Resistance                    | For Active discharge mode enabled option                               |      | 200  |     | Ω     |

| K <sub>AOT</sub>     | Adaptive-On-Time Constant                         | $t_{ON} = K_{AOT} x (V_{OUT}/V_{IN}), Fsw = 500kHz,$<br>$V_{OUT} = 5V$ |      | 2100 |     | ns    |

|                      |                                                   | Fsw = 300kHz                                                           |      | 300  |     |       |

| Fsw <sup>8</sup>     | Switching Frequency Factory Trim Options          | Fsw = 500kHz                                                           |      | 500  |     | 1     |

|                      |                                                   | Fsw = 800kHz                                                           |      | 800  |     | kHz   |

|                      | •                                                 | Fsw = 1000kHz                                                          |      | 1000 |     |       |

| tss_delay            | Vout Soft-Start Delay                             | EN = Low to High                                                       |      | 2    |     | ms    |

|                      |                                                   | VOUT = 5V                                                              |      | 8    |     | 1     |

| V <sub>OUT_RR</sub>  | V <sub>ОUТ</sub> Soft-Start Ramp Rate             | VOUT = 3.3V                                                            |      | 4    |     | mV/μs |

| . 001_1(10           | Too. Son State Camp Nate                          | VOUT = 1.8V                                                            |      | 3    |     | 1, 50 |

| V <sub>OUT_PG</sub>  | Output Voltage Power-Good Threshold               | Percentage of nominal Vout                                             | 85   |      | 115 | %     |

<sup>7.</sup> Device is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range by design, characterization and correlation with statistical process controls.

<sup>8.</sup> Switching frequency is factory trimmed options, please refer to ordering information to select relevant part.

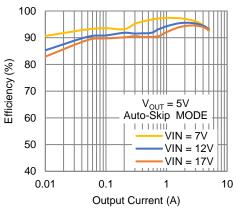

## **Typical Characteristics**

Unless otherwise noted,  $V_{IN} = 12V$ ,  $F_{SW} = 500kHz$ , and  $T_A = 25$ °C.

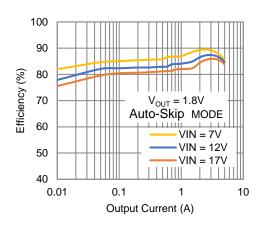

# **Efficiency vs Output Current**

#### **Efficiency vs Output Current** $(L1 = 2.2\mu H, Fsw = 500kHz)$

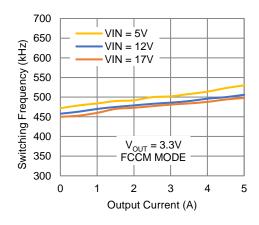

## **Switching Frequency vs. Output Current**

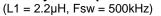

# **Efficiency vs Output Current**

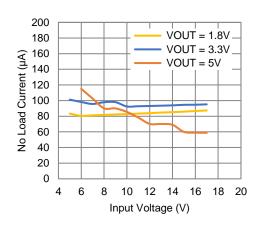

### No Load Input Supply Current vs VIN

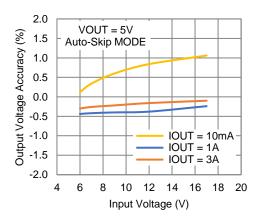

#### Line Regulation ( $V_{OUT} = 5V$ , Auto-Skip Mode)

# Typical Characteristics (continued)

Unless otherwise noted,  $V_{IN} = 12V$ ,  $F_{SW} = 500kHz$ , and  $T_A = 25$ °C.

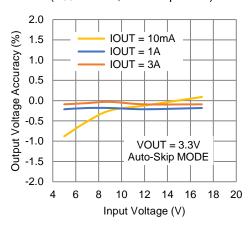

#### **Line Regulation**

(Vout = 3.3V, Auto-Skip Mode)

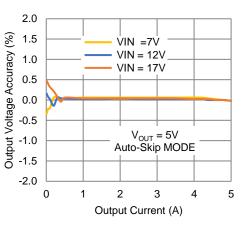

#### **Load Regulation**

(V<sub>OUT</sub> = 5V, Auto-Skip Mode)

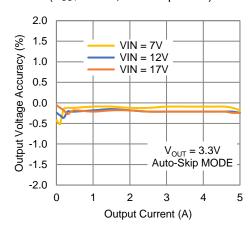

#### Load Regulation

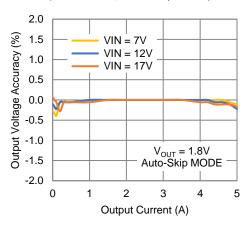

(Vout = 1.8V, Auto-Skip Mode)

#### **Line Regulation**

(Vout = 1.8V, Auto-Skip Mode)

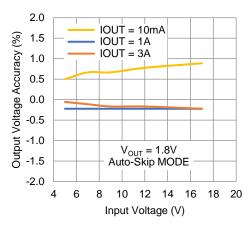

#### **Load Regulation**

(V<sub>OUT</sub> = 3.3V, Auto-Skip Mode)

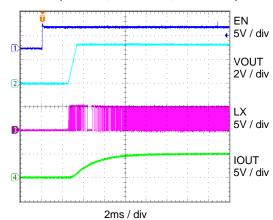

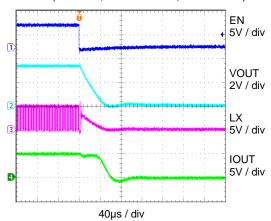

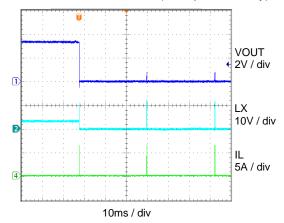

### Soft Start with EN

$(V_{IN} = 5V, Vout=3.3V, I_{OUT} = 5.0A)$

# **Typical Characteristics (continued)**

Unless otherwise noted,  $V_{IN} = 12V$ ,  $F_{SW} = 500kHz$ , and  $T_A = 25$ °C.

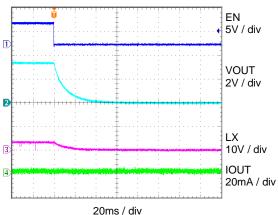

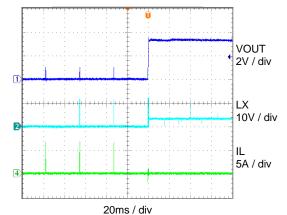

#### Shutdown with EN

$(V_{IN} = 5V, V_{OUT} = 3.3V, I_{OUT} = 5.0A)$

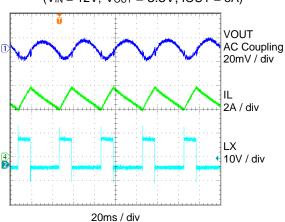

### **Output Voltage Ripple**

$(V_{IN} = 12V, V_{OUT} = 3.3V, IOUT = 5A)$

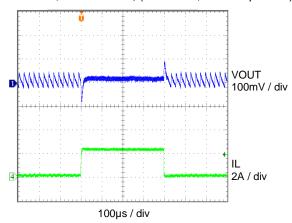

#### **Load Transient**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ , (1.5A-4.5A, Auto-Skip Mode)

### **Output Active Discharge**

$(V_{IN} = 12V, V_{OUT} = 3.3V, I_{OUT} = 0mA)$

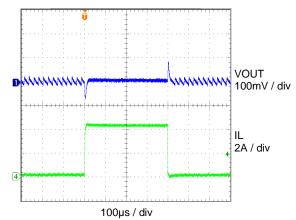

#### **Load Transient**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ , (0.1A-2.5A, Auto-Skip Mode)

#### **Load Transient**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ , (0A-4.5A, Auto-Skip Mode)

# **Typical Characteristics (continued)**

Unless otherwise noted,  $V_{IN} = 12V$ ,  $F_{SW} = 500kHz$ , and  $T_A = 25$ °C.

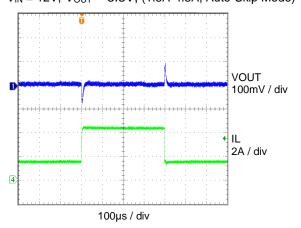

## **Output Short Protection Entry**

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 3.3V, (Hiccup Mode Entry)

## **Output Short Protection Recovery**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ , (Hiccup Mode Recovery)

## **Functional Description**

KTB8372 is a highly efficient, high-performance, monolithic buck regulator that operates from an input voltage of 4.7V to 18V and can output up to 5A. It integrates the main switch, synchronous rectifier switch, PWM control circuitry, Vout setting DAC, and various protection features.

#### **Control Scheme**

KTB8372 uses a proprietary adaptive on-time (AOT) PWM control scheme to maintain a nearly constant switching frequency as input voltage and output voltage vary. Compared to typical current-mode PWM schemes, the AOT control scheme provides quick response to line and load transients with excellent stability and wide bandwidth, thereby minimizing output voltage droop and soar for dynamic loads, even with minimal output capacitance. The adaptive on-time approximates fixed-frequency switching without using a fixed clock oscillator, which eliminates the need to wait for the next clock before responding to a load transient.

KTB8372 feedback loop also adds a proprietary, internally compensated, integrating error amplifier to remove the output voltage offset normally associated with other AOT, constant on-time (COT), and hysteretic architectures.

#### Shutdown Mode

When the EN pin is low, KTB8372 is in shutdown mode and draws extremely low supply current.

#### **Fnable**

KTB8372 buck regulator is turned on and off using the EN pin. Pull EN pin high to enable the buck regulator and pull the EN pin low to disable the buck regulator.

#### **Soft-Start**

KTB8372 contains soft-start circuitry to ramp up  $V_{\text{OUT}}$  slowly in order to reduce inrush current at  $V_{\text{IN}}$  and prevent the inductor current from reaching the peak current limit during startup. During soft start, the ramp up rate of  $V_{\text{OUT}}$  is regulated to a constant value, which can be found in table 1.

**Table 1. Output Voltage Ramp Rate**

| Nominal Output Voltage Setting (Vout) | VOUT ≤ 2.2V | 2.2V < VOUT ≤ 3.3V | 3.3V < VOUT ≤ 5.5V |

|---------------------------------------|-------------|--------------------|--------------------|

| Soft-Start Ramp Rate<br>(Vout_RR)     | 40mV/μs     | 60mV/μs            | 100mV/μs           |

The soft-start time can be estimated by: tss = Vout / Vout\_RR

#### **Auto-Skip Mode and Forced-PWM Mode.**

KTB8372 has a default automatic skip mode. In the automatic skip mode, KTB8372 transit automatically between constant frequency PWM mode at heavy loads and PFM mode at light loads. Auto-Skip mode is helpful for applications that need high efficiency at light loads. While skipping, single pulses are evenly spaced, resulting in the lowest output ripple and noise when compared to competing "pulse-grouping" or "burst mode" devices.

In applications that are sensitive to audio noise, an Ultrasonic Mode option is available<sup>9</sup>. When the KTB8730 enters PFM frequency during single - pulse skipping the switching frequency will remain above the audio frequency band (20Hz to 20kHz) at very light loads.

In applications that are noise sensitive, even at light load conditions, fixed switching frequency is also desired. and the KTB8372 needs to operate in forced PWM mode. A Forced-PWM mode option is available

#### **Active Discharge Option**

KTB8372 features an active discharge option, where a  $200\Omega$  (typical) on-chip resistor is connected between the LX and PGND pins. This resistor discharges the output capacitor through the inductor when KTB8372 is disabled. KTB8372 can be factory trimmed to Active Discharge. Please contact Kinetic Technologies representative for ordering information.

<sup>9.</sup> Contact your local sales representative.

## Input Under-Voltage Lockout (UVLO)

When the input voltage  $(V_{IN})$  is below the under-voltage lockout threshold  $(V_{UVLO})$ , the buck is disabled. When  $V_{IN}$  rises above  $V_{UVLO}$ , and if the buck is enabled, the default soft-start ramp begins.

### **Over-Current Protection (OCP)**

KTB8372 features high-side switch peak-current limit and low-side switch valley-current limit, which protect the integrated FETs and inductor during over-current faults. The current limits control the buck's switching on a cycle-bycycle basis and have a higher priority than the regulation threshold and adaptive on-time. When either high-side or low-side FET current reaches their respective over-current limiting threshold, high-side FET is turned off and will be kept off for at least 50ns, while low-side FET is turned on. The high-side FET can only be turned back on until the low-side FET current drops below the valley current limit. During sustained over-current faults, the output voltage typically droops below the regulation threshold.

### **Output Short-Circuit Protection**

During an over-current event, when 8 consecutive (interval time minimum than 2µs typical) OCP events are detected, KTB8372 will enter hiccup mode and pause all switching. The buck regulator attempts to soft-start after 20ms, if the fault persists, the buck regulator once again enters hiccup mode and periodically re-attempts soft-start until the fault is removed. The low duty-factor during hiccup mode prevents the IC from getting hot.

#### **Thermal Shutdown**

KTB8372 is turned off by an internal thermal shutdown when the junction temperature exceeds the thermal shutdown threshold (150°C typical). The device restarts when the junction temperature drops by 20°C.

### **Trim Options**

KTB8372 are factory trimmed using one-time programmable (OTP) registers. Standard versions are available for various default output voltage settings and modes – see the *Ordering Information* section. Contact Kinetic Technologies local representative for availability of versions with alternative default settings.

## **Applications Information**

#### Recommended Inductors

The selection of the inductor affects the steady-state operation as well as transient behavior and loop stability. The three most important inductor specifications to consider are inductor value, DC resistance (DCR), and saturation current rating. Higher inductance gives lower inductor current ripple, while lower inductance usually gives faster load transient response. KTB8372 is trimmed for inductors with nominal inductance of 0.8µH to 6.5µH. Select an inductor with a saturation current rating that is higher than KTB8372 peak current limit. Also, choose an inductor with sufficient temperature-rise current rating to satisfy the RMS load-current of the application. Consider the inductor's resistance, since these will affect the efficiency. Larger physical case-sizes, good winding designs, and better magnetic materials can increase efficiency.

#### **Recommended Capacitors**

Ceramic input and output capacitors with X5R or X6S or X7R are recommended due to their low ESR, low ESL, low temperature coefficients, and small physical sizes. Consider the voltage rating, size, and DC bias derating characteristic of the capacitor

#### **Input Capacitor**

Choose an input capacitor with voltage rating of 25V or more,  $10\mu F$  nominal capacitance or more, and 0805 case-size or larger. Larger values and larger case-size provide more effective capacitance when considering the DC bias derating characteristic of the capacitor. If the application's input voltage is supplied through a connector or a cable, add additional bypass capacitance where  $V_{IN}$  first arrives to the PCB.

#### **Output Capacitors**

Choose output capacitors with voltage rating of 10V or more,  $22\mu F$  total nominal capacitance or more, and 0805 case-size or larger. Consider the  $V_{OUT}$  setting of the regulator and how case size has a significant impact on DC bias derating. At high  $V_{OUT}$  settings, more total nominal capacitance is needed to achieve the same effective capacitance compared to lower  $V_{OUT}$  settings.

For the very best possible load transient response, use multiple capacitors in parallel to achieve sufficient total effective output capacitance:

$$C_{OUT_{EFFECTIVE}} \ge \frac{L \times I_{STEP}}{33m\Omega \times (V_{IN} - V_{OUT})}$$

where  $I_{STEP}$  is the largest load transient step in the application, and  $33m\Omega$  is constant set by internal control circuit. Please note that the above formula is already guard-banded by a margin of 2x to accommodate capacitor and inductor tolerances and the variability of a transient arrival time with respect to the switching cycle of the regulator.

If needed, the total effective output capacitance can be distributed by placing additional capacitors remotely at the point of load. In applications where transient performance is less critical, especially when  $V_{\text{IN}}$  minus  $V_{\text{OUT}}$  is small, it is acceptable to reduce the total effective output capacitance to save board space and cost at the expense of load transient droop and soar.

As a design example, consider a system with  $V_{IN} = 12V$  (min),  $V_{OUT} = 1.8V$ , and  $I_{STEP} = 5A$  (max):

$$C_{OUT_{EFFECTIVE}} \geq \frac{1\mu H \times 5A}{33m\Omega \times (12V-1.8V)} \cong 15\mu F$$

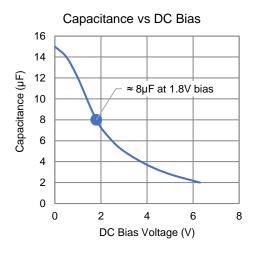

In this example, choose output capacitors with total effective capacitance of  $14\mu\text{F}$  or more at a DC bias of 1.8V. A single  $15\mu\text{F}$  capacitor will not be enough when considering its DC bias characteristic, per Figure 1. At 1.8V bias, it retains only about  $8\mu\text{F}$ ; therefore, for best transient response, use two of these capacitors in parallel for a total effective capacitance of  $16\mu\text{F}$ .

Figure 1. Typical DC Bias Derating Characteristic an Example 15µF Ceramic Capacitor.

December 2023 – Revision 4a Page 11 of 13 Kinetic Confidential

## **Recommended PCB Layout**

KTB8372 PCB layout is optimized for small footprint, low EMI, and good performance. The example follows the below PCB layout recommendations:

- Connect the input capacitor C<sub>IN</sub> as close as possible to the VIN and PGND pins using top-side thick metal traces.

- 2. Connect the ground terminals of output capacitors C<sub>OUT</sub> as close as possible to the ground terminal of C<sub>IN</sub> and the PGND pins using top-side metal.

- 3. Connect the Boost capacitor as close as possible to the Boost pin and Lx pin of the chip.

- 4. Connect the local top side PGND island to the PCB ground plane using multiple parallel vias.

- 5. Do not connect the AGND pins directly to the top side PGND. Instead, connect the AGND pins to the PCB ground plane using their own vias.

- 6. Connect the inductor to the LX pins with a wide trace.

- 7. Connect the Vout terminals of the inductor to the output capacitors with a wide and short trace.

- 8. Route the V<sub>OUT</sub> sense trace from C<sub>OUT</sub> to the VOUT pin with care to keep it away from noisy traces, especially the LX trace. Additionally, use ground fill to shield noise from coupling into the V<sub>OUT</sub> sense.

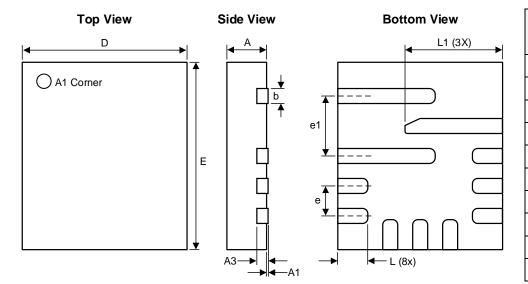

# **Packaging Information**

## UQFN2.22.5-11 (2.2mm x 2.5mm x 0.55mm)

| Dimension | mm        |      |      |  |  |

|-----------|-----------|------|------|--|--|

| Dimension | Min.      | Тур. | Max. |  |  |

| Α         | 0.50      | 0.55 | 0.60 |  |  |

| A1        | 0.00      | 0.02 | 0.05 |  |  |

| А3        | 0.150 REF |      |      |  |  |

| b         | 0.15      | 0.20 | 0.25 |  |  |

| D         | 2.10      | 2.20 | 2.30 |  |  |

| E         | 2.40      | 2.50 | 2.60 |  |  |

| е         | 0.40 BSC  |      |      |  |  |

| e1        | 0.80 BSC  |      |      |  |  |

| L         | 0.35      | 0.40 | 0.45 |  |  |

| L1        | 1.25      | 1.30 | 1.35 |  |  |

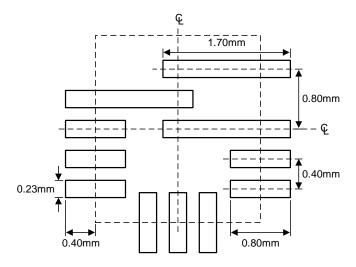

## **Recommended Footprint**

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.