# USB D+/D- Hi-Speed or SBU1/2 Switch with Fault Protection

### **Features**

- Operating Range: 2.7V to 5.5V

- For USB D+/D- Hi-Speed or SBU1/2 signals

- USB Hi-Speed Dual SPDT Switch/MUX

- Reverse blocking back-to-back MOSFETs

- ► >1GHz -3db Bandwidth

- Low 6Ω Switch On-Resistance

- Typical 4.0pF Switch On-Capacitance

- Overvoltage Protection

- ► Up to +20VDC

- ► Surge Protection Up to +25V

- FLAG open drain output overvoltage indicator

- EN to disable switch output

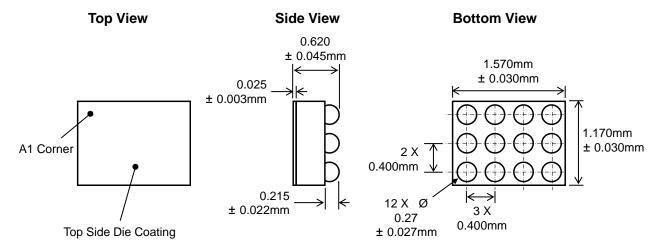

- WLCSP34-12 package (1.17mm x 1.57mm)

- -40°C to +85°C Temperature Range

# Applications

Mobile Internet Devices

Tablet Computers

Peripherals

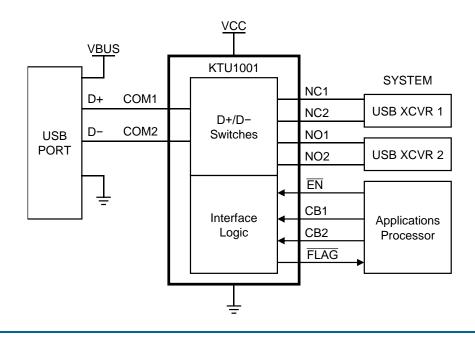

**Typical Application**

Smartphones

• USB Type-C

## **Brief Description**

The KTU1001 is a Hi-Speed (up to 480Mbps) USB dual SPDT (single-pole/double-throw) switch with overvoltage protection. This device operates over a 2.7V to 5.5V input supply range with over voltage fault protection up to 20V. USB Type-C features high voltage charging where the KTU1001 protects USB data lines from short circuit and surge events that can permanently damage the mobile system. The device features independent control bits for each switch pair and an on/off enable ( $\overline{EN}$ ) for shutdown mode. Additional features include low switch on resistance and capacitance along with a fault flag ( $\overline{FLAG}$ ) to alert the system processor to overvoltage fault events.

Similar in features and performance to KTU1000, the KTU1001 adds reverse blocking MOSFET switch functionality.

The KTU1001 has low power consumption and is available in an ultra-small 12-Bump 1.17mm x 1.57mm WLCSP package making it an ideal solution for USB interface switching and protection in mobile applications.

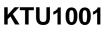

### **Pin Descriptions**

| Pin # | Name | Function                                                                                                                    |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------|

| A1    | CB1  | Digital Control Input 1                                                                                                     |

| A2    | COM2 | Common Terminal for I/O Switch 1 (Connect to D+, D-, SBU1 or SBU2)                                                          |

| A3    | COM1 | Common Terminal for I/O Switch 2 (Connect to D-, D+, SBU1 or SBU2)                                                          |

| A4    | FLAG | Active low fault flag output signal to alert fault event                                                                    |

| B1    | VCC  | Input Supply Voltage input pin                                                                                              |

| B2    | CB2  | Digital Control Input 2                                                                                                     |

| B3    | GND  | Ground. Connect this pin to system ground.                                                                                  |

| B4    | ĒN   | Active low enable input. Drive EN to a logic high level to disable the device and place switches to a high impedance state. |

| C1    | NO2  | Normally Open Terminal for USB I/O Switch 2                                                                                 |

| C2    | NO1  | Normally Open Terminal for USB I/O Switch 1                                                                                 |

| C3    | NC2  | Normally Closed Terminal for USB I/O Switch 2                                                                               |

| C4    | NC1  | Normally Closed Terminal for USB I/O Switch 1                                                                               |

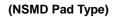

### WLCSP34-12

12-Bump 1.17mm x 1.57mm x 0.62mm WLCSP Package

### Top Mark

WW = Device ID Code, XX = Date Code, YY = Assembly Code, ZZZZ = Serial Number

# Absolute Maximum Ratings<sup>1</sup>

### $(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol                                                             | Description                              | Value     | Units |  |

|--------------------------------------------------------------------|------------------------------------------|-----------|-------|--|

| VCC                                                                | Input voltage                            | -0.3 to 8 | V     |  |

| CB1, CB2, EN, FLAG                                                 | CB1, CB2, EN, FLAG CB1, CB2, EN, FLAG    |           | V     |  |

| 00144 00140                                                        | I/O Voltage (2.7V < Vcc < 5.5V)          | -1 to 20  | V     |  |

| COM1, COM2                                                         | Surge IEC61000-4-5                       | 25        | V     |  |

| NO1, NO2, NC1, NC2                                                 | NO1, NO2, NC1, NC2 I/O Voltage           |           | V     |  |

| Ts                                                                 | Ts Storage Temperature Range             |           | °C    |  |

| T <sub>LEAD</sub> Maximum Soldering Temperature (at leads, 10 sec) |                                          | 260       | °C    |  |

| Isw Switch I/O Current (Continuous)                                |                                          | 25        | mA    |  |

| Ts                                                                 | T <sub>s</sub> Storage Temperature Range |           | °C    |  |

| T <sub>LEAD</sub> Maximum Soldering Temperature (at leads, 10 sec) |                                          | 260       | °C    |  |

# **Thermal Capabilities**

| Symbol | Description                                           | Value | Units |

|--------|-------------------------------------------------------|-------|-------|

| θ」Α    | Thermal Resistance – Junction to Ambient <sup>2</sup> | 74    | °C/W  |

| PD     | Maximum Power Dissipation at $T_A \le 25^{\circ}C$    | 1697  | mW    |

# **Ordering Information**

| Part Number   | Marking                 | Operating<br>Temperature | Package  |

|---------------|-------------------------|--------------------------|----------|

| KTU1001EVA-TR | LOXXYYZZZZ <sup>3</sup> | -40°C to +85°C           | WLCSP-12 |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

<sup>3.</sup> XX = Date Code, YY = Assembly Code, ZZZZ = Serial Number.

# **Electrical Characteristics**<sup>4</sup>

| Unless otherwise noted, the Min and Max specs are applied over the full operation temperature ran  | je of |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| -40°C to +85°C, while Typical values are specified at room temperature (25°C). Vcc = 2.7V to 5.5V. |       |  |  |  |  |  |

| Symbol                       | Description                          | Conditions                                                                                                                                         |     | Тур  | Max  | Units |

|------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| General Op                   | perating Conditions                  |                                                                                                                                                    | •   | •    | •    |       |

| Vcc                          | Input operating range                |                                                                                                                                                    |     |      | 5.5  | V     |

| $V_{sw}$                     | Analog V <sub>IO</sub> Signal Range  | Vcc = 2.7V to 5.5V                                                                                                                                 |     |      | VFP  | V     |

| V <sub>UVLO</sub>            | Under Voltage Lockout Threshold      |                                                                                                                                                    |     | 2.0  | 2.5  | V     |

| Icc                          | Quarte Quarte                        | $V_{CC} = 3.0V, V_{EN} = V_{CC}$                                                                                                                   |     | 0.1  | 1    | μA    |

|                              | Supply Current                       | $V_{CC} = 3.0V, V_{CB} = V_{CC}, V_{EN} = 0V$                                                                                                      |     | 25   | 35   | μA    |

| .,                           | COM Overvoltage Detect<br>Threshold  | Vcc = 3.0V, VIN rising                                                                                                                             |     | 4.8  | 5.1  | V     |

| $V_{FP}$                     |                                      | V <sub>CC</sub> = 3.0V, VIN falling                                                                                                                |     | 4.3  |      | V     |

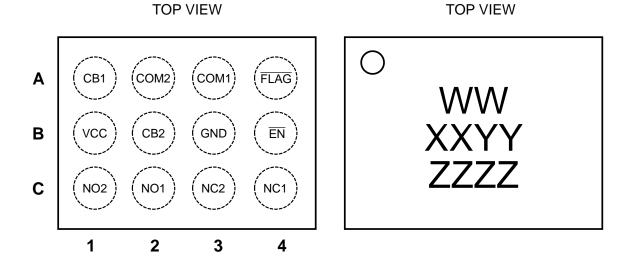

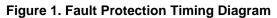

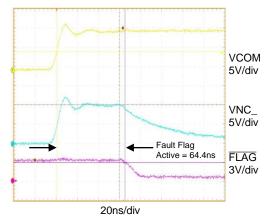

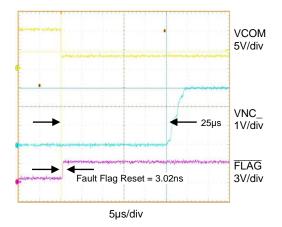

| t <sub>FP</sub>              | Fault Protection Response Time       | $V_{COM} = 1V$ to 10V step, Vcc = 3.0V; Figure 1                                                                                                   |     |      | 100  | ns    |

| t <sub>FPR</sub>             | Fault Protection Recovery Time       | $V_{COM} = 10V$ to 1V step, Vcc = 3.0V; Figure 1                                                                                                   |     | 26   |      | us    |

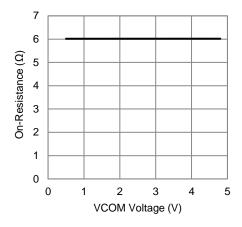

| Ron                          | On-Resistance                        | V <sub>COM</sub> = 0V to V <sub>CC</sub> , I <sub>COM</sub> = 10mA                                                                                 |     | 6.0  | 9.0  | Ω     |

| RON[MATCH]                   | On-Resistance Match between channels | $V_{COM} = 0V$ to $V_{CC}$ , $I_{COM} = 10$ mA                                                                                                     |     |      | 0.3  | Ω     |

| Ron[FLAT]                    | On-Resistance Flatness               | $V_{COM} = 0V$ to $V_{CC}$ , $I_{COM} = 10mA$                                                                                                      |     |      | 0.45 | Ω     |

| ICOM_(OFF)                   | COM_ Off Leakage Current             | $\label{eq:Vcc} \begin{array}{l} V_{CC} = V_{EN} = 3.0V, \ V_{COM} = 3.0V \ \text{or} \ 0V, \\ V_{NC} = 0V \ \text{or} \ 3.0V \end{array}$         |     | ±3   | ±10  | μΑ    |

| INC_(OFF)                    | NC_ Off Leakage Current              | $\label{eq:VCC} \begin{array}{l} V_{CC} = V_{EN} = 3.0V, \ V_{COM} = 3.0V \ \text{or} \ 0V, \\ V_{NC} = 0V \ \text{or} \ 3.0V \end{array}$         |     | ±0.1 | ±1   | μΑ    |

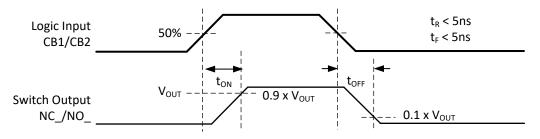

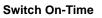

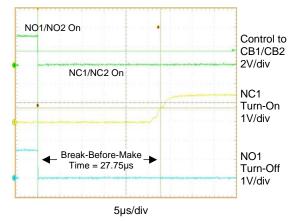

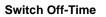

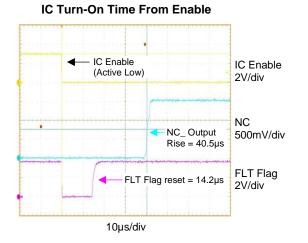

| Timing – Fi                  | igures 2 and 3                       |                                                                                                                                                    |     |      |      |       |

|                              | IC Wake-Up Turn On Time              | $\label{eq:VCC} \begin{array}{l} V_{CC}=3.0V, \ V_{COM}=1.5V, \ R_L{=}50\Omega, \ V_{EN}=0V, \\ V_{CB}=0V \ to \ V_{CC}, \ Figure \ 3 \end{array}$ |     | 14   | 30   | μs    |

| t <sub>ON[SW]</sub>          | SW Transition Turn On Time           | $V_{CC} = 3.0V$ , $V_{COM} = 1.5V$ , $R_L=50\Omega$ , $V_{EN} = 0V$ , $V_{CB} = 0V$ to $V_{CC}$ , Figure 2a                                        |     | 28   | 60   | μs    |

| toff[sw]                     | SW Transition Turn Off Time          | $V_{CC} = 3.0V$ , $V_{COM} = 1.5V$ , $R_L = 50\Omega$ ,<br>$V_{EN} = 0V$ , $V_{CB} = 0V$ to $V_{CC}$ , Figure 2a                                   |     | 1    |      | μs    |

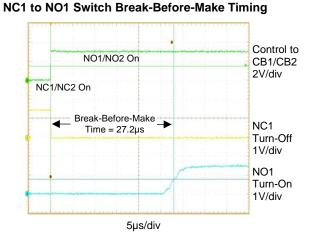

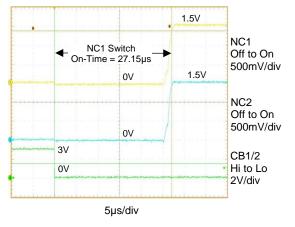

| tD                           | Break-Before-Make Time Delay         | $R_L = 50\Omega$                                                                                                                                   |     | 28   |      | μS    |

| $C_{\text{COM}(\text{OFF})}$ | Off Capacitance                      | $V_{COM} = 0.5 V_{P-P}$ , DC bias = 0V, f = 1MHz                                                                                                   |     | 4.5  |      | pF    |

| CCOM(ON)                     | On Capacitance                       | $V_{COM} = 0.5 V_{P-P}$ , DC bias = 0V, f = 240MHz                                                                                                 |     | 4    |      | pF    |

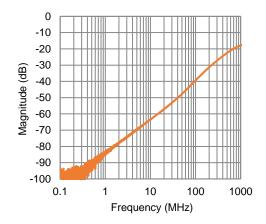

| AC Performa                  | ance                                 |                                                                                                                                                    |     |      |      |       |

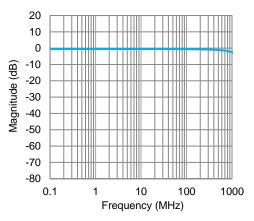

| BW                           | -3dB Bandwidth                       | $R_S = R_L = 50\Omega$ , $V_{COM} = 0dBm$                                                                                                          |     | >1   |      | GHz   |

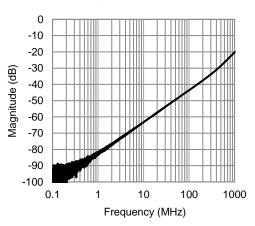

| Viso                         | Off Isolation                        | $f = 100 \text{kHz}, V_{\text{COM}} = 0.5 V_{\text{p-p}}, R_{\text{S}} = R_{\text{L}} = 50 \Omega$                                                 |     | -70  |      | dB    |

| V <sub>CT</sub>              | Crosstalk                            | $f = 100 \text{kHz}, V_{COM} = 0.5 V_{p-p}, R_S = R_L = 50 \Omega$                                                                                 |     | -80  |      | dB    |

| Logic Input,                 | Enable, CB1, CB2                     |                                                                                                                                                    |     |      |      |       |

| Vih                          | Input Logic High                     |                                                                                                                                                    | 1.2 |      |      | V     |

| VIL                          | Input Logic Low                      |                                                                                                                                                    |     |      | 0.4  | V     |

| $I_{LK_{IN}}$                | Input Leakage Current                | $\overline{EN} = CB_{-} = 0V \text{ or } V_{CC}$                                                                                                   | -1  |      | 1    | μA    |

| Fault Flag                   |                                      | •                                                                                                                                                  |     | •    | •    |       |

| V <sub>OL</sub>              | FLAG Output Voltage Low              | V <sub>IO</sub> = 3.3V, I <sub>SINK</sub> = 1mA                                                                                                    |     | 0.1  | 0.4  | V     |

| ILK_OUT                      | FLAG Output Leakage Current          | $V_{IO} = 3.3V$ , FLAG de-asserted                                                                                                                 | -1  |      | 1    | μA    |

<sup>4.</sup> KTU1001 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range by design, characterization and correlation with statistical process controls.

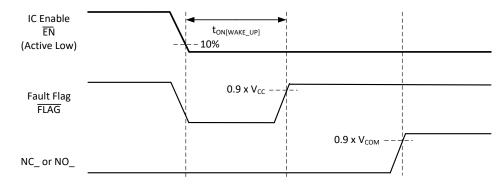

### **Timing Diagrams**

Figure 2b. Switch Timing Test Circuit

Figure 3. IC Wake-Up Timing Diagram

# **Enable and Control Input Truth Table**

| Control Logic Inputs |     |     | Switch Status |      |  |

|----------------------|-----|-----|---------------|------|--|

| EN                   | CB1 | CB2 | COM1          | COM2 |  |

| 0                    | 0   | 0   | NC1           | NC2  |  |

| 0                    | 0   | 1   | NC1           | NO2  |  |

| 0                    | 1   | 0   | NO1           | NC2  |  |

| 0                    | 1   | 1   | NO1           | NO2  |  |

| 1                    | Х   | Х   | OPEN          | OPEN |  |

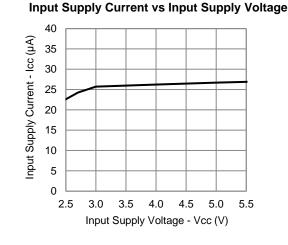

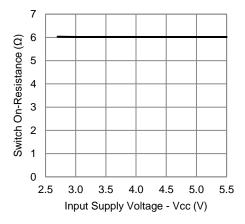

### **Typical Characteristics**

VCC = 3V,  $C_{VCC} = 1\mu F$ ,  $T_{AMB} = 25^{\circ}C$  unless otherwise specified.

Switch On-Resistance vs Input Supply Voltage

Frequency Response - Off Isolation

#### Switch On-Resistance vs COM Voltage

**Frequency Response - On Loss**

**Frequency Response - Crosstalk**

# **Typical Characteristics (continued)**

VCC = 3V,  $C_{VCC} = 1\mu F$ ,  $T_{AMB} = 25^{\circ}C$  unless otherwise specified.

#### COM Input OVP to NC/NO Output Shutdown Fault Flag Reporting Time

### COM Input OVP to NC/NO Output Recovery Time

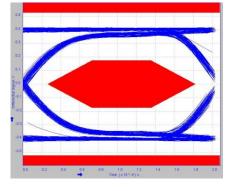

# **Typical Characteristics (continued)**

VCC = 3V,  $C_{VCC} = 1\mu F$ ,  $T_{AMB} = 25^{\circ}C$  unless otherwise specified.

### Eye Diagram USB 2.0 High-Speed

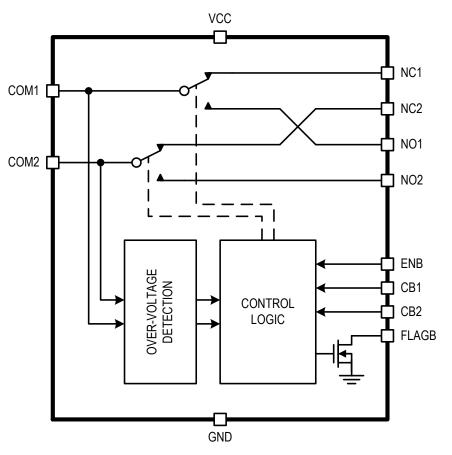

### **Functional Block Diagram**

Figure 4. Functional Block Diagram

### **Functional Description**

The KTU1001 is a SPDT analog switch intended for 2:1 MUX operation for USB 2.0 Low (LS), Full (FS), High Speed (HS) and Display Port AUX channel applications. This device is specified to operate over a 2.7V to 5.5V input supply range. An active logic low enable pin ( $\overline{EN}$ ) along with two switch state control pins (CB1 and CB2) provide full control of IC functions. When the device is disabled, the quiescent current consumption drops to less than 1µA. Upon IC enable, supply quiescent current increases to a typical 25µA to save power in battery powered portable products. The default enable SPDT switch state is normally closed between the COM1/2 pins and the NC1/2 pins unless otherwise programmed via the CB1/2 pins. Refer to the IC control truth table for all programming logic states.

The NC\_ and NO\_ switch pairs utilize break-before-make switching to assure the COM1/2 inputs are only passed to one switch output pair at any given time. When switch pairs are toggled to the opposite output via the CB1/2 control pins, the on-switch will open with a typical 28µs delay before the off-switchs close.

The USB switch inputs COM1 and COM2 are over voltage protected with fixed typical OVP threshold level at 4.8V regardless of the applied Vcc supply voltage. Should a voltage level greater than the OVP threshold be applied to either COM1 or COM2, the IC will disable the switches to NC\_ or NO\_ and place them in a high impedance state to protect the device and down steam USB controller from damage. An active-low fault flag output (FLAG) is provided to alert the system controller to the fault condition.

### **Application Information**

### Analog Switch Applications

The KTU1001 is intended for use as a USB 2:1 data mux for USB 2.0 Low, Full and Hi-Speed applications up to 480Mbps and has an analog bandwidth up to 1GHz. KTU1001 switches may be used for other AC coupled analog signal switching applications as long as applied signal levels are within the minimum to maximum V<sub>SW</sub> operating limits as defined in the electrical characteristics specification for this device. Due to the high frequency nature of USB and similar data signals, unused switch inputs or output should be terminated with 50 $\Omega$  to ground to prevent unwanted signal-line reflections.

### **Reverse-Blocking Switches**

The switches in the KTU1001 are reverse-blocking, using back-to-back MOSFET switches in each path. When the switches are OFF, current is blocked in both directions from NO1, NO2, NC1, or NC2 to COM1 or COM2. This allows more system flexibility for USB transceivers or other I/O devices connected in the system, it is not necessary to control the state of disabled channels NO1, NO2, NC1, or NC2.

For lower Rdson and capacitance, please refer to KTU1000.

### Input Supply Bypass Capacitor

The KTU1001 may be operated with no additional external components. To maximize Hi-Speed data performance in systems with voltage supply noise or ripple, adding a Vcc input bypass capacitor in the range of 0.1uF or 1uF from V<sub>cc</sub> to GND is recommended. Ceramic capacitors with minimum voltage rating of 6.3V and X5R or X7R dielectric should be used.

### **PCB Layout Guidelines**

To achieve adequate bandwidth in USB 2.0 Hi-Speed data applications, careful PCB layout is critical for the signal traces to the COM1, COM2, NC1, NC2, NO1, and NO2 pins. The following guidelines are recommended for best system performance:

- 1. Multi-layer printed circuits boards are recommended for hi-speed data communication applications. Best USB signal quality is realized with 4 layer or greater PCB assemblies. A multilayer board minimizes the board material thickness between the signal trace layer and adjacent ground plane layer, which aids in maintaining consistant trace impedance for high-frequency signals.

- Input and Output data signals should utilize matched width and length traces and be made as short as possible. As a general guide, USB 2.0 Hi-Speed signals, traces should be equal in lengths, maintain a 6 mil width with 8 mil spacing between traces and have 30 mil or greater isolation to adjacent signal traces.

- 3. The use of data trace vias should be minimized or ideally avoided altogether as they introduce impedance discontinuities at high frequencies and compromise signal quality.

- 4. If signal traces require turns or bends, do not use 90° turns. To maintain good high frequency performance, trace turns should use rounded arcs or bend at 45° angles at a maximum.

- 5. All signal traces should be routed directly over ground planes placed on the next PCB layer. To maintain best PCB trace impedance characteristic and minimize electro-magnetic interfearance (EMI), the ground plane layer should have no breaks under the signal trace layer. The ground plane layer should be referenced back to the system power source ground at one single point to avoid stray current paths through the ground plane.

## **Packaging Information**

### WLCSP34-12 (1.570mm x 1.170mm x 0.620mm)

### **Recommended Footprint**

\* Dimensions are in millimeters.

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.