# Programmable Dual Output Power Supply

#### **Features**

- Input voltage range (2.7V to 5.5V)

- Dual output regulator with single inductor

- High efficiency above 85%

- Charge pump with PFM mode at light load

- Programmable output voltages

- · Positive output voltage range

- ► +4.0V to +6.3V (100mV/step)

- Negative output voltage range

-4.0V to -6.3V (100mV/step)

- Programmable regulator offset voltage

- 1.0% output voltage accuracy

- Output current up to +200mA, -150mA

- · Programmable active discharge

- I<sup>2</sup>C compatible interface

- 1 μA shutdown supply current

- Pb-free WLCSP-15 package

- -40°C to +85°C Temperature Range

# **Applications**

- Smartphone or Tablet TFT-LCD

- Operational Amplifiers

- Audio Amplifier Power

- Digital to Analog converters

- · General Dual Power Supply Applications

# **Brief Description**

The KTZ8812 is a dual output power supply IC used in portable appliances where both a positive and negative supply is required. The positive and negative output rails provide bias supplies for TFT LCD panels, OPA, Audio Amplifiers, DAC etc. The device only requires a single inductor, thereby minimising the total PCB area.

It features an integrated step-up DC-DC converter with input voltage range from 2.7V to 5.5V. An LDO and charge pump generate dual regulated outputs, whose voltages can be programmed via an I<sup>2</sup>C compatible interface. Optimized step-up, LDO and charge pump converters maximize conversion efficiency, exceeding 85%.

KTZ8812 integrates all compensation and soft-start circuitry, which results in a simpler and smaller solution with much fewer external components. High switching frequency (1.8MHz) allows the use of a smaller inductor and capacitor to further reduce the solution size.

The I<sup>2</sup>C compatible interface allows control of the positive and negative outputs from +4.0V to +6.3V and from -4.0V to -6.3V, respectively, as well as programming additional registers on the device.

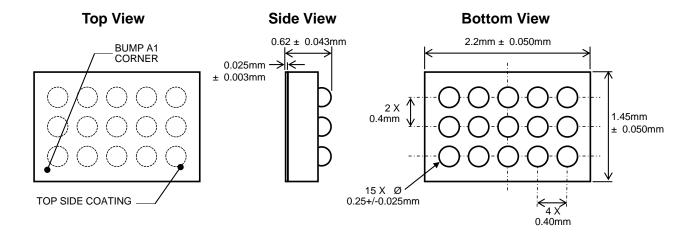

KTZ8812 is available in a RoHS compliant 15-bump 2.2mm x 1.45mm x 0.62mm WLCSP.

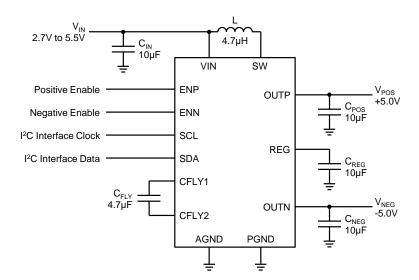

# **Typical Application**

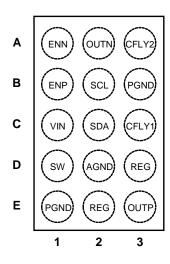

# **Pin Descriptions**

| Pin #<br>(WLCSP-15) | Pin #<br>(TDFN-14) | Name  | Function                                                    |

|---------------------|--------------------|-------|-------------------------------------------------------------|

| A1                  | 14                 | ENN   | Enable input pin for negative output (OUTN)                 |

| A2                  | 1                  | OUTN  | Charge pump output pin of the negative power                |

| A3                  | 2                  | CFLY2 | Negative charge pump flying capacitor pin                   |

| B1                  | 12                 | ENP   | Enable input pin for positive power (OUTP)                  |

| B2                  | 13                 | SCL   | SCL Clock input pin of the I <sup>2</sup> C interface       |

| B3, E1              | 3, 8               | PGND  | Power GND connection                                        |

| C1                  | 10                 | VIN   | Input supply pin for the IC                                 |

| C2                  | 11                 | SDA   | SDA bi-direction data pin of the I <sup>2</sup> C interface |

| C3                  | 4                  | CFLY1 | Negative charge pump flying capacitor pin                   |

| D1                  | 9                  | SW    | Switch node pin of step-up converter                        |

| D2                  | 5                  | AGND  | Analog ground                                               |

| D3, E2              | 6                  | REG   | Step-up converter output pin                                |

| E3                  | 7                  | OUTP  | Positive LDO output pin                                     |

# WLCSP-15

TOP VIEW TOP VIEW

15-Bump 2.2mm x 1.45mm x 0.62mm WLCSP Package

# **Top Mark**

$XX = \text{Device Code} \\ YY = \text{Date Code}, \ ZZ = \text{Assembly Code}$

# Absolute Maximum Ratings<sup>1</sup>

# $(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol             | Description                | Value              | Units                    |    |

|--------------------|----------------------------|--------------------|--------------------------|----|

| VIN                | Input voltage              |                    | -0.3 to 6                | V  |

| SW                 | High voltage switching     | DC Voltage         | -0.3 to 7                | V  |

| 377                | node                       | Transient Voltage  | -0.3 to 7.7 <sup>2</sup> | V  |

| CFLY1              | Charge pump pin            |                    | -0.3 to 7                | V  |

| OUTP, REG          | Output voltage pin         |                    | -0.3 to 7                | V  |

| OUTN, CFLY2        | Output voltage pin and cl  | harge pump voltage | -7 to 0.3                | V  |

| ENP, ENN, SCL, SDA | Control pins               | Control pins       |                          | V  |

| TJ                 | Operating Temperature F    | Range              | -40 to 150               | °C |

| Ts                 | Storage Temperature Ra     | -65 to 150         | °C                       |    |

| TLEAD              | Maximum Soldering Tem      | 300                | °C                       |    |

| ESD                | HBM electrical static disc | charge             | 2.0                      | kV |

# **Thermal Capabilities**

| Symbol              | Description                                           | Value | Units |

|---------------------|-------------------------------------------------------|-------|-------|

| θЈА                 | Thermal Resistance – Junction to Ambient <sup>3</sup> | 77    | °C/W  |

| PD                  | Maximum Power Dissipation at T <sub>A</sub> = 25°C    | 1.3   | W     |

| ΔΡ <sub>D</sub> /ΔΤ | Derating Factor Above T <sub>A</sub> = 25°C           | -13   | mW/°C |

# **Ordering Information**

| Part Number    | Marking <sup>4</sup> | I <sup>2</sup> C Device<br>Address | V <sub>POS</sub> Default Setting | V <sub>NEG</sub><br>Default<br>Setting | Operating<br>Temperature | MSL     | Package  |

|----------------|----------------------|------------------------------------|----------------------------------|----------------------------------------|--------------------------|---------|----------|

| KTZ8812EUO-TR  | IRYYZZ               | 3Eh                                | +5.0V                            | -5.0V                                  | -40°C to +85°C           | Level 1 | WLCSP-15 |

| KTZ8812BEUO-TR | MEYYZZ               | 4Eh                                | +5.0V                            | -5.0V                                  | -40°C to +85°C           | Level 1 | WLCSP-15 |

December 2017 - Revision 04b Page 3 Company Confidential

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Transient voltage rating is with 300ns maximum duration and 50% maximum duty cycle.

<sup>3.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

<sup>4. &</sup>quot;YYZZ" is the date code and assembly code.

# Electrical Characteristics<sup>5</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, while *Typ* values are specified at room temperature (25°C).  $V_{IN} = 3.7V$ , ENN = ENP =  $V_{IN}$ ,  $V_{POS} = +5V$ ,  $V_{NEG} = -5V$ .

| Symbol               | Description                           | Conditions                                     | Min  | Тур  | Max  | Units |

|----------------------|---------------------------------------|------------------------------------------------|------|------|------|-------|

| IC Supply            |                                       |                                                |      | •    |      |       |

| VIN                  | Input operating range                 |                                                | 2.7  |      | 5.5  | V     |

| UVLO                 | Input under voltage lockout           | Rising VIN                                     |      |      | 2.5  | V     |

| UVLO <sub>HYST</sub> | UVLO hysteresis                       |                                                |      | 0.2  |      | V     |

|                      | IC standby current                    | Not switching                                  |      | 620  |      | μΑ    |

| lα                   | IC operating current                  | Switching, no load                             |      | 1.2  |      | mA    |

| I <sub>SHDN</sub>    | Shutdown current                      | ENP = ENN = 0V,<br>SDA = SCL = V <sub>IN</sub> |      | 0.1  |      | μА    |

| Step-Up Do           | C-DC Converter                        |                                                |      |      |      |       |

| I <sub>LIM</sub>     | Peak NMOS current limit               |                                                | 0.9  |      |      | Α     |

| Fsw                  | Oscillator frequency                  |                                                |      | 1.8  |      | MHz   |

| D <sub>max</sub>     | Maximum duty cycle                    |                                                | 80   | 86   |      | %     |

| Ts                   | Start-up time                         |                                                |      | 0.7  |      | ms    |

| OUTP Posi            | tive Output VPOS                      | •                                              |      | _    |      |       |

| V <sub>POS</sub>     | Positive output voltage range         |                                                | 4.0  |      | 6.3  | V     |

| V <sub>POS_ACC</sub> | Positive output voltage accuracy      | T <sub>A</sub> = 25°C                          | -1.0 |      | +1.0 | %     |

| I <sub>LIM_POS</sub> | Positive output current limit         |                                                | 200  |      |      | mA    |

| V <sub>DROP</sub>    | Dropout voltage                       | I <sub>ОUТ</sub> = 150mA                       |      | 150  |      | mV    |

| VLINE                | Line regulation                       | $\Delta V_{OUT} = 1V,$ $I_{OUT} = 30mA$        |      | 0.06 |      | %/V   |

| V <sub>LOAD</sub>    | Load regulation                       | Δ <b>I</b> <sub>OUT</sub> = 80mA               |      | 6    |      | mV    |

| Rdischarge           | Discharge resistance                  |                                                |      | 70   |      | Ω     |

| OUTN Neg             | ative Output VNEG                     |                                                |      |      |      |       |

| V <sub>NEG</sub>     | Negative output voltage range         |                                                | -4.0 |      | -6.3 | V     |

| V <sub>NEG_ACC</sub> | Negative output voltage accuracy      | T <sub>A</sub> = 25°C                          | -1.0 |      | +1.0 | %     |

| ILIM_NEG             | Negative output max regulated current |                                                | 150  |      |      | mA    |

| $F_{\text{SW\_CP}}$  | Charge pump switching frequency       |                                                |      | 0.9  |      | MHz   |

| $V_{LINE}$           | Line regulation                       | $\Delta V_{OUT} = 1V,$ $I_{OUT} = 30mA$        |      | 0.02 |      | %/V   |

| VLOAD                | Load regulation                       | $\Delta I_{OUT} = 80 \text{mA}$                |      | 14   |      | mV    |

| RDISCHARGE           | Discharge resistance                  |                                                |      | 20   |      | Ω     |

| Logic Conf           | rol: ENP, ENN                         |                                                |      |      |      |       |

| $V_{TH	ext{-L}}$     | ENP, ENN pin logic low threshold      | V <sub>IN</sub> = 2.5V to 5.5V                 |      |      | 0.4  | V     |

| V <sub>TH-H</sub>    | ENP, ENN pin logic high threshold     |                                                | 1.4  |      |      | V     |

| R <sub>ENP</sub>     | ENP pull down resistor                |                                                |      | 500  |      | kΩ    |

| R <sub>ENN</sub>     | ENN pull down resistor                |                                                |      | 500  |      | kΩ    |

<sup>5.</sup> KTZ8812 is guaranteed to meet performance specifications over the  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range by design, characterization and correlation with statistical process controls.

December 2017 - Revision 04b Page 4 Company Confidential

# Electrical Characteristics<sup>5</sup>

| Symbol                | Description                                                     | Conditions | Min | Тур | Max | Units |

|-----------------------|-----------------------------------------------------------------|------------|-----|-----|-----|-------|

| I <sup>2</sup> C-Comp | patible Voltage Specifications (SCL, SDA)                       | •          |     |     |     |       |

| VIL                   | Input Logic Low Threshold                                       | SDA, SCL   |     |     | 0.4 | V     |

| VIH                   | Input Logic High Threshold                                      | SDA, SCL   | 1.2 |     |     | V     |

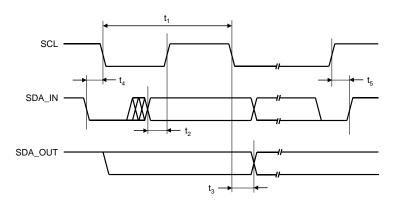

| I <sup>2</sup> C-Comp | patible Timing Specifications (SCL, SDA) <sup>6</sup> , see Fig | ure 1      |     |     |     |       |

| t <sub>1</sub>        | SCL (Clock Period)                                              |            | 2.5 |     |     | μS    |

| t <sub>2</sub>        | Data In Setup Time to SCL High                                  |            | 100 |     |     | ns    |

| <b>t</b> 3            | Data Out Stable After SCL Low                                   |            | 0   |     |     | ns    |

| <b>t</b> <sub>4</sub> | SDA Low Setup Time to SCL Low (Start)                           |            | 100 |     |     | ns    |

| t <sub>5</sub>        | SDA High Hold Time After SCL High (Stop)                        |            | 100 |     |     | ns    |

| fsclk                 | SCL Clock Frequency                                             |            |     |     | 400 | kHz   |

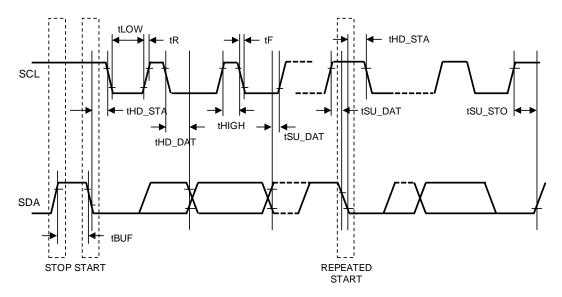

| t <sub>BUF</sub>      | Bus Free Time Between a STOP and START Condition                |            | 1.3 |     |     | μS    |

| thd_sta               | Hold Time (Repeated) START Condition <sup>6</sup>               |            | 0.6 |     |     | μS    |

| t <sub>LOW</sub>      | LOW Period of SCL Clock                                         |            | 1.3 |     |     | μS    |

| thigh                 | HIGH Period of SCL Clock                                        |            | 0.6 |     |     | μS    |

| t <sub>SU_STA</sub>   | Setup Time for a Repeated START Condition                       |            | 0.6 |     |     | μS    |

| thd_dat               | Data Hold Time <sup>7</sup>                                     |            | 0   |     | 0.9 | μS    |

| t <sub>SU_DAT</sub>   | Data Setup Time <sup>6</sup>                                    |            | 100 |     |     | ns    |

| t <sub>R</sub>        | Rise Time of Both SDA and SCL Signals                           |            |     |     | 300 | ns    |

| t <sub>F</sub>        | Fall Time of Both SDA and SCL Signals                           |            |     |     | 300 | ns    |

| tsu_sto               | Setup Time for STOP Condition                                   |            | 0.6 |     |     | μS    |

| Thermal               | Shutdown                                                        |            |     |     |     |       |

| т                     | IC junction thermal shutdown threshold                          |            |     | 140 |     | °C    |

| $T_{J-TH}$            | IC junction thermal shutdown hysteresis                         |            |     | 15  |     | °C    |

December 2017 - Revision 04b Page 5 Company Confidential

<sup>6.</sup> A fast-mode device can be used in a standard-mode system, but the requirement tSU\_DAT = to 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tR max + tSU\_DAT = 1000 + 250 = 1250nsec before the SCL line is released.

<sup>7.</sup> A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIHMIN of the SCL signal) to bridge the undefined region of the falling edge of SCL.

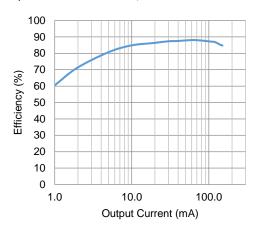

# **Typical Characteristics**

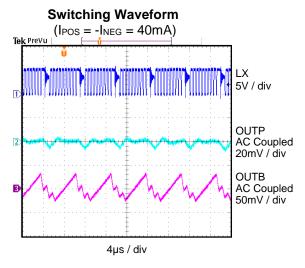

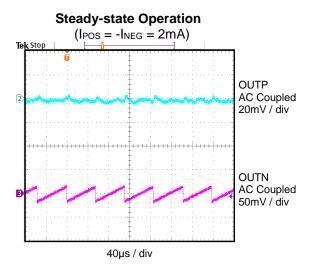

$V_{IN} = 3.7V$ ,  $L = 4.7\mu H$  (Coilcraft LPS4018-472),  $C_{IN} = C_{REG} = C_{POS} = C_{NEG} = 10\mu F$ ,  $I_{POS} = -I_{NEG} = 40mA$ ,  $I_{POS} = 25^{\circ}C$  unless otherwise specified. Default setting:  $I_{POS} = -I_{NEG} = 40mA$ ,  $I_{POS} = -I_{NEG} =$

#### **Efficiency vs. Output Current**

$(V_{POS}/V_{NEG} = +/-5.0V, V_{REG} Offset = 300mV)$

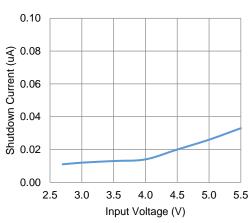

# **Shutdown Current**

(ENP = ENN = low)

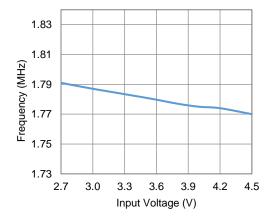

## Frequency Vs Vin

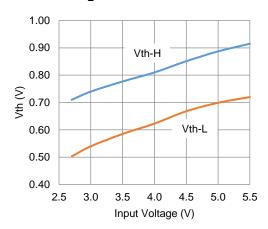

## **EN Logic Threshold Vth Vs Vin**

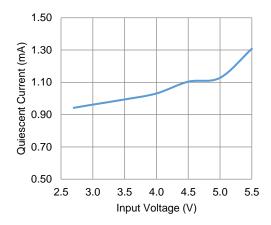

#### **Quiescent Current Vs Vin**

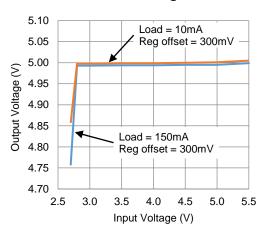

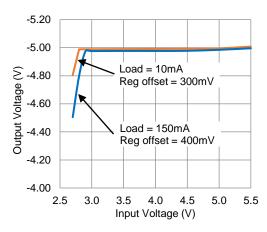

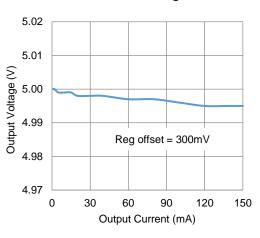

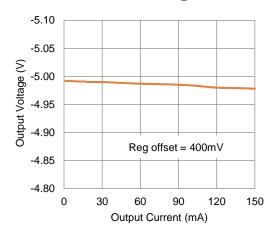

# **Typical Characteristics**

$V_{IN} = 3.7V$ ,  $L = 4.7\mu H$  (Coilcraft LPS4018-472),  $C_{IN} = C_{REG} = C_{POS} = C_{NEG} = 10\mu F$ ,  $I_{POS} = -I_{NEG} = 40mA$ ,  $I_{POS} = 25^{\circ}C$  unless otherwise specified. Default setting:  $I_{POS} = -I_{NEG} = 40mA$ ,  $I_{POS} = -I_{NEG} =$

#### **OUTP Line Regulation**

## **OUTN Line Regulation**

## **OUTP Load Regulation**

## **OUTN Load Regulation**

# **Typical Characteristics**

$V_{IN} = 3.7V$ ,  $L = 4.7\mu H$  (Coilcraft LPS4018-472),  $C_{IN} = C_{REG} = C_{POS} = C_{NEG} = 10\mu F$ ,  $I_{POS} = -I_{NEG} = 40mA$ ,  $I_{POS} = 25^{\circ}C$  unless otherwise specified. Default setting:  $I_{POS} = -I_{NEG} = 40mA$ ,  $I_{POS} = -I_{NEG} =$

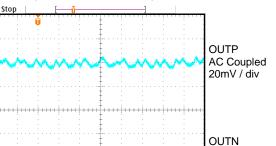

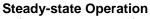

# Steady-state Operation (IPOS = -INEG = 10mA)

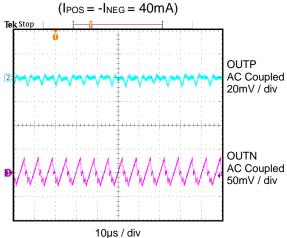

# Load Transient

10µs / div

(10mA to 150mA step load)

AC Coupled

50mV / div

Figure 1. I<sup>2</sup>C Compatible Interface Timing

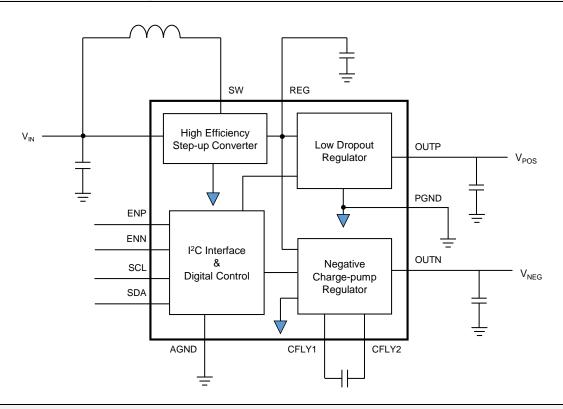

# **Functional Block Diagram**

# **Functional Description**

The KTZ8812, powered from single-cell Li-Ion/Polymer batteries from 2.7V to 5.5V, is a dual output converter only requiring a single inductor. The KTZ8812 is a dual switching converter to generate both a positive and a negative power supplies that are required by TFT-LCD display panels, high power audio amplifiers, operational amplifiers and DACs. The KTZ8812 integrates a boost regulator, LDO and charge pump, to generate two regulated output rails OUTP and OUTN, whose voltages can be adjusted by I<sup>2</sup>C compatible interface. The step-up converter generates a positive voltage on the REG pin that is used by both the positive output and negative output converters. The internal LDO gets its power from the REG pin, drops down the voltage with optimized high efficiency linear control, delivering the positive supply (OUTP). The negative supply (OUTN) is generated by an integrated inverting voltage regulator charge pump driven from the step-up converter output.

December 2017 - Revision 04b Page 9 Company Confidential

The REG offset voltage, equal to the voltage between REG and the Max (OUTP, -OUTN), can be set to 300mV and 400mV depending on the maximum output currents on OUTP and OUTN. Higher output current requires higher offset voltage (headroom) in order to guarantee the best regulation. By adjusting the offset voltage to the lower level 300mV, the overall converter efficiency can be optimized for the application. The device can operate with independent current setting on each output, even with no load on one output and full load on the other.

The device integrates full compensation and soft-start circuitry, which results in a simpler and smaller solution with fewer external components. High switching frequency (1.8MHz) allows the use of a smaller inductor and capacitors to further reduce the solution size.

## **Under Voltage Lockout (UVLO)**

The KTZ8812 integrates an Under Voltage Lockout circuit to prevent the IC from operating until  $V_{IN}$  pin exceeds the UVLO threshold. Output voltages will not be activated until enable signals are applied. All of the internal converters will be disabled as soon as the  $V_{IN}$  voltage falls below the UVLO threshold minus the UVLO hysteresis (UVLOHYST).

#### **Active Discharge**

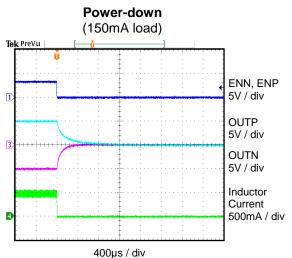

The positive rail OUTP and/or the negative rail OUTN can be actively discharged by KTZ8812. The output discharge settings can be programmed by the I<sup>2</sup>C interface; the default value is ON. When the supply output is powered down, KTZ8812 will discharge the corresponding output(s) through the associated R<sub>DISCHARGE</sub> resistor connected to ground. The power-down happens when both enable signals (ENN, ENP) go low, or when one enable goes low while the other enable is already low. If one output is turned OFF while the other output stays ON, the discharge circuit is inactive for both outputs.

#### **Step-Up DC-DC Converter Operation**

The step-up converter uses a current mode design operating at 1.8 MHz in full load, allowing the use of small value 4.7µH inductors. The converter dynamically adjusts the output to optimize the highest efficiency depending on OUTP and OUTN voltage requirements.

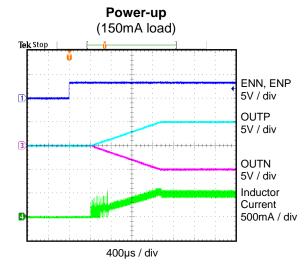

#### **Power-Up and Soft-Start**

The step-up converter operates when either enable signal, ENN or ENP, is pulled high or I<sup>2</sup>C bits are set, and VIN voltage is greater than UVLO. If the enable signal is already high when VIN reaches the UVLO threshold, the step-up converter will start switching immediately. An integrated soft-start circuit controls excessive inrush current from the battery during startup.

#### **Power-Down**

The step-up converter powers down when VIN goes below UVLO minus UVLO<sub>HYST</sub> or after both OUTP and OUTN have been disabled, if VIN is still above UVLO.

#### **LDO Regulator Operation (OUTP)**

The internal LDO gets its power from the REG pin and drops down the voltage, generating the positive voltage rail OUTP. The LDO's ripple rejection characteristics help to filter the output of the boost converter in order to provide a well-controlled supply.

#### Power-Up and Soft-Start (OUTP)

The LDO is activated immediately when ENP signal is asserted, and VIN voltage is above the UVLO threshold and the step-up converter has reached its target voltage. OUTP has a soft-start circuit which slowly ramps-up its output.

# **Power-Down and Discharge (OUTP)**

The LDO stops operating when VIN drops below the UVLO threshold minus the hysteresis, or when ENP is deasserted. The positive supply output can be actively discharged to GND through the IC's R<sub>DISCHARGE</sub> internal resistor. The discharge selection bit by default is ON, and can be reset or set through register programming.

#### **Setting the Output Voltage (OUTP)**

The output voltage of the LDO is programmable via an I<sup>2</sup>C compatible interface with 5 bits, from 4.0V to 6.3V with 100mV steps.

December 2017 - Revision 04b Page 10 Company Confidential

## Regulated Inverting Charge Pump Operation (OUTN)

The inverting charge pump generates the negative voltage rail OUTN from the output voltage of the boost converter (VREG). The converter uses a four-switch topology with single external flying capacitor to generate the negative output voltage. The first switching phase turns on two of the switches to charge the flying capacitor equal to VREG, and the second phase inverts the drive logic of all four switches, negatively connecting the flying capacitor to OUTN.

## Power-Up and Soft-Start (OUTN)

The charge pump is activated immediately when ENN signal is asserted, and VIN voltage is above the UVLO threshold and the step-up converter has reached its target voltage. OUTN has a soft-start circuit which slowly ramps-up its output.

## Power-Down and Discharge (OUTN)

The charge pump stops operating when VIN drops below the UVLO threshold minus UVLO hysteresis or when the ENN is de-asserted. The negative rail can be actively discharged to GND during power-down if required. A discharge selection bit is available to enable or disable this function.

## **Setting the Output Voltage (OUTN)**

The output voltage of the charge pump is programmable via an I<sup>2</sup>C compatible interface with 5 bits, from -4.0V to -6.3V with 100mV steps.

#### Flying Capacitor Selection (OUTN)

The charge pump needs an external flying capacitor with a minimum value of 4.7µF. Ceramic X5R dielectric material or better is recommended for best performance. For proper operation, the flying capacitor value must be lower than the output capacitor of the boost converter on VREG pin.

#### **Thermal Shutdown**

A thermal shutdown feature is included in the KTZ8812. When the IC's junction temperature (T<sub>J</sub>) reaches 140°C, the IC will immediately enter shutdown mode. Once T<sub>J</sub> drops 15°C to approximately 125°C, the IC will resume normal operation.

#### I<sup>2</sup>C interface or Enable Control

The KTZ8812 can be turned on/off by pulling the ENP/ENN inputs high without using the I<sup>2</sup>C interface. If the I<sup>2</sup>C interface is not used, both SDA and SCL inputs should be tied high (for example to VIN directly) or through pull-up resistors. These two inputs should never be left floating (unconnected).

KTZ8812 can be controlled via the I<sup>2</sup>C interface, even when both the ENP and ENN inputs are low.

# **Application Information**

#### I<sup>2</sup>C Serial Data Bus

Figure 2. I<sup>2</sup>C Mode Timing Diagram

The KTZ8812 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the bus is called a master, whereas the devices controlled by the master are known as slaves. A master device must generate the serial clock (SCL), control bus access and generate START and STOP conditions to control the bus. The KTZ8812 operates as a slave on the I<sup>2</sup>C bus. Within the bus specifications a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The KTZ8812 works in both modes. Connections to the bus are made through the open-drain I/O lines SDA and SCL.

The following bus protocol has been defined (Figure 2 and Figure 3):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH.

Changes in the data line while the clock line is high are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

## **Bus Not Busy**

Both data and clock lines remain HIGH.

## Start Data Transfer

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

#### Stop Data Transfer

A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

#### Data Valid

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

December 2017 - Revision 04b Page 12 Company Confidential

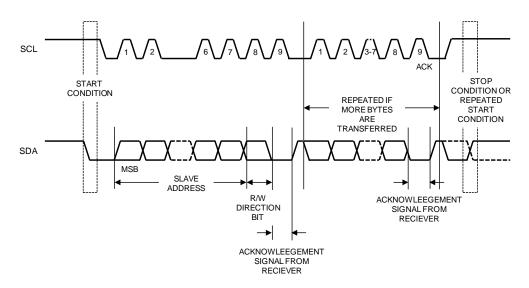

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited, and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

#### Acknowledge

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

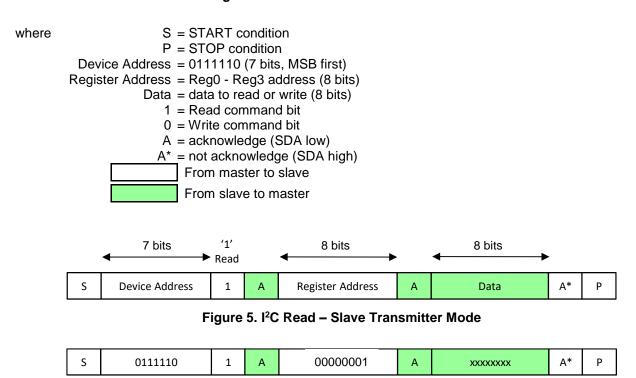

Figure 3. Data Transfer on I<sup>2</sup>C Serial Bus

Depending upon the state of the R/W bit, two types of data transfer are possible:

- Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first.

- 2. Data transfer from a slave transmitter to a master receiver. The master transmits the first byte (the slave address). The slave then returns an acknowledge bit, followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data is transferred with the most significant bit (MSB) first.

The KTZ8812 can operate in the following two modes:

1. Slave Receiver Mode (Write Mode): Serial data and clock are received through SDA and SCL. After each byte is received an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit (see Figure 4 for Interface). The slave address byte is the first byte received after the master generates the START condition. The slave address byte contains

December 2017 - Revision 04b Page 13 Company Confidential

- the 7- KTZ8812 address followed by the direction bit (R/W), which, for a write, is 0. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. After the KTZ8812 acknowledges the slave address + write bit, the master transmits a register address to the KTZ8812. This sets the register pointer on the KTZ8812. The master may then transmit zero or more bytes of data, with the KTZ8812 acknowledging each byte received. The address pointer will increment after each data byte is transferred. The master generates a STOP condition to terminate the data write.

- 1. Slave Transmitter Mode (Read Mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the KTZ8812 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer. The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit KTZ8812 address followed by the direction bit (R/W), which, for a read, is 1. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. The KTZ8812 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The KTZ8812 must receive a "not acknowledge" to end a read.

The 7-bit slave device address of KTZ8812 is 0111110 binary (or 3Eh), KTZ8812B is 1001110 binary (or 4Eh).

Figure 4. I<sup>2</sup>C Write - Slave Receiver Mode

Figure 6. Example of Read Command

# I<sup>2</sup>C Serial Bus Register Map

The device has four registers, Reg0 to Reg3. Each register includes one data byte (8 bits) that can be written or read via the I<sup>2</sup>C interface.

|   | VPOS: Reg 0     |  |  |  |  |

|---|-----------------|--|--|--|--|

| 0 | VPOS            |  |  |  |  |

| 1 | OUTP Voltage    |  |  |  |  |

| 2 | Setting         |  |  |  |  |

| 3 | 4.0V to 6.4V in |  |  |  |  |

| 4 | 100mV steps     |  |  |  |  |

| 5 |                 |  |  |  |  |

| 6 | Reserved*       |  |  |  |  |

| 7 |                 |  |  |  |  |

|   | VNEG: Reg 1       |  |  |  |  |

|---|-------------------|--|--|--|--|

| 0 | VNEG              |  |  |  |  |

| 1 | OUTN Voltage      |  |  |  |  |

| 2 | Setting           |  |  |  |  |

| 3 | -4.0V to -6.4V in |  |  |  |  |

| 4 | -100mV steps      |  |  |  |  |

| 5 |                   |  |  |  |  |

| 6 | Reserved*         |  |  |  |  |

| 7 |                   |  |  |  |  |

|   |                   |  |  |  |  |

|   | Control 2: Reg 2 |                      |  |  |  |  |  |

|---|------------------|----------------------|--|--|--|--|--|

|   | 0                | Reset Control        |  |  |  |  |  |

|   | 1                | Reset Control        |  |  |  |  |  |

|   | 2                | Reset                |  |  |  |  |  |

|   | თ                | CP PFM Enable        |  |  |  |  |  |

|   | 4                | Slow Soft Start Ramp |  |  |  |  |  |

|   | 5                |                      |  |  |  |  |  |

|   | 6                | Reserved*            |  |  |  |  |  |

|   | 7                |                      |  |  |  |  |  |

| Э | a "(             | )" in these bits.    |  |  |  |  |  |

|   | Control 1: Reg 3   |

|---|--------------------|

| 0 | Discharge OUTN     |

| 1 | Discharge OUTP     |

| 2 | EN Standby         |

| 3 | ENP                |

| 4 | ENN                |

| 5 |                    |

| 6 | REG Offset Setting |

| 7 |                    |

Note: \* When writing to a register, always write a "0" in these bits.

| Reg# | Register Name                           | Address (Hex) | Default Value (Hex)<br>(Reset Value) |

|------|-----------------------------------------|---------------|--------------------------------------|

| Reg0 | VPOS (positive voltage output) Register | 00            | 90                                   |

| Reg1 | VNEG (negative voltage output) Register | 01            | 90                                   |

| Reg2 | Control 2 Register                      | 02            | 08                                   |

| Reg3 | Control 1 Register                      | 03            | 43                                   |

# VPOS Positive Voltage Output Setting Register (ADDR 00h, Default 0Ah)

$\ensuremath{\text{V}_{\text{POS}}}$  Voltage Setting 4.0V to 6.3V in 100mV steps.

$V_{POS} = 4.0V + (code * 100mV).$

| Bit-7    | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| Reserved |       | VPOS  | VPOS  | VPOS  | VPOS  | VPOS  |       |

| OUTP Output Voltage |           |     |             |  |  |  |  |

|---------------------|-----------|-----|-------------|--|--|--|--|

| Dec                 | Binary    | Hex | Voltage (V) |  |  |  |  |

| 0                   | 0000 0000 | 00h | 4.0         |  |  |  |  |

| 1                   | 0000 0001 | 01h | 4.1         |  |  |  |  |

| 2                   | 0000 0010 | 02h | 4.2         |  |  |  |  |

| 3                   | 0000 0011 | 03h | 4.3         |  |  |  |  |

| 4                   | 0000 0100 | 04h | 4.4         |  |  |  |  |

| 5                   | 0000 0101 | 05h | 4.5         |  |  |  |  |

| 6                   | 0000 0110 | 06h | 4.6         |  |  |  |  |

| 7                   | 0000 0111 | 07h | 4.7         |  |  |  |  |

| 8                   | 0000 1000 | 08h | 4.8         |  |  |  |  |

| 9                   | 0000 1001 | 09h | 4.9         |  |  |  |  |

| 10                  | 0000 1010 | 0Ah | 5.0         |  |  |  |  |

| 11                  | 0000 1011 | 0Bh | 5.1         |  |  |  |  |

| 12                  | 0000 1100 | 0Ch | 5.2         |  |  |  |  |

| 13                  | 0000 1101 | 0Dh | 5.3         |  |  |  |  |

| 14                  | 0000 1110 | 0Eh | 5.4         |  |  |  |  |

| 15                  | 0000 1111 | 0Fh | 5.5         |  |  |  |  |

| 16                  | 0001 0000 | 10h | 5.6         |  |  |  |  |

| 17                  | 0001 0001 | 11h | 5.7         |  |  |  |  |

| 18                  | 0001 0010 | 12h | 5.8         |  |  |  |  |

| 19                  | 0001 0011 | 13h | 5.9         |  |  |  |  |

| 20                  | 0001 0100 | 14h | 6.0         |  |  |  |  |

| 21                  | 0001 0101 | 15h | 6.1         |  |  |  |  |

| 22                  | 0001 0110 | 16h | 6.2         |  |  |  |  |

| 23                  | 0001 0111 | 17h | 6.3         |  |  |  |  |

## **VNEG Negative Voltage Output Setting Register (ADDR 01h, Default 0Ah)**

$V_{NEG}$  Voltage Setting -4.0V to -6.3V in 100mV steps.  $V_{NEG}$  = -4.0V - (code \* 100mV).

| Bit-7    | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| Reserved |       |       | VNEG  | VNEG  | VNEG  | VNEG  | VNEG  |

|     | OUTN Output Voltage |     |             |  |  |  |  |  |

|-----|---------------------|-----|-------------|--|--|--|--|--|

| Dec | Binary              | Hex | Voltage (V) |  |  |  |  |  |

| 0   | 0000 0000           | 00h | -4.0        |  |  |  |  |  |

| 1   | 0000 0001           | 01h | -4.1        |  |  |  |  |  |

| 2   | 0000 0010           | 02h | -4.2        |  |  |  |  |  |

| 3   | 0000 0011           | 03h | -4.3        |  |  |  |  |  |

| 4   | 0000 0100           | 04h | -4.4        |  |  |  |  |  |

| 5   | 0000 0101           | 05h | -4.5        |  |  |  |  |  |

| 6   | 0000 0110           | 06h | -4.6        |  |  |  |  |  |

| 7   | 0000 0111           | 07h | -4.7        |  |  |  |  |  |

| 8   | 0000 1000           | 08h | -4.8        |  |  |  |  |  |

| 9   | 0000 1001           | 09h | -4.9        |  |  |  |  |  |

| 10  | 0000 1010           | 0Ah | -5.0        |  |  |  |  |  |

| 11  | 0000 1011           | 0Bh | -5.1        |  |  |  |  |  |

| 12  | 0000 1100           | 0Ch | -5.2        |  |  |  |  |  |

| 13  | 0000 1101           | 0Dh | -5.3        |  |  |  |  |  |

| 14  | 0000 1110           | 0Eh | -5.4        |  |  |  |  |  |

| 15  | 0000 1111           | 0Fh | -5.5        |  |  |  |  |  |

| 16  | 0001 0000           | 10h | -5.6        |  |  |  |  |  |

| 17  | 0001 0001           | 11h | -5.7        |  |  |  |  |  |

| 18  | 0001 0010           | 12h | -5.8        |  |  |  |  |  |

| 19  | 0001 0011           | 13h | -5.9        |  |  |  |  |  |

| 20  | 0001 0100           | 14h | -6.0        |  |  |  |  |  |

| 21  | 0001 0101           | 15h | -6.1        |  |  |  |  |  |

| 22  | 0001 0110           | 16h | -6.2        |  |  |  |  |  |

| 23  | 0001 0111           | 17h | -6.3        |  |  |  |  |  |

## Control Register 2 (ADDR 02h, Default 08h)

#### Reset

This register controls the Reset Mode. To reset the device, Bit [0] or Bit [1] = 1 and bit [2] = 1.

#### **I2C Disable**

It is possible to disable the I2C interface in shutdown mode (when ENP = ENN = low) by previously setting Bit [0] = 1 and Bit [2] = 0. The benefit is that the KTZ8812 shutdown current is zero.

Once the device is in "zero current shutdown mode", it does no longer respond to I2C commands. The KTZ8812 must be restarted by transitioning at least one of the enable input, ENP or ENN, from low to high.

## **CP PFM Enable**

Enable PFM mode at light loads for the Charge-Pump. Default is ON (1).

For highest efficiency, the charge pump operates in PFM mode at low current on negative output.

To minimize the output ripple under light load condition, PFM mode can be disabled.

## **Slow Soft Start Ramp**

The soft start ramp can be set to two different values. Normal soft start time is 1.3ms to ramp to  $\pm$ -5V outputs. The ramp can be slowed down 7 times to 9.3ms to ramp outputs to  $\pm$ -5V. Default is normal ramp (1).

| Bit-7 | Bit-6 | Bit-5 | Bit-4                                               | Bit-3                                            | Bit-2                                                | Bit-1                                                                                   | Bit-0                   |

|-------|-------|-------|-----------------------------------------------------|--------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------|

| 0     | 0     | 0     | Slow Soft Start<br>Ramp<br>0 = Slower<br>1 = Normal | CP PFM Enable  0 = Disable  1 = Enable (Default) | 100 = Do n<br>101 = Rese<br>110 = Rese<br>111 = Rese | Nothing (Defa<br>othing (bit 2 c<br>et Registers or<br>et Main Digital<br>et Complete C | leared)<br>nly<br>⊢only |

|       |       |       | (Default)                                           |                                                  | I2C Disable 001 = I2C disable mode                   |                                                                                         |                         |

<sup>\*</sup> When writing to the register, always write "0" in the reserved bits.

For example, to disable the CP PFM mode, write 0x00 in the Control register.

## Control Register 1 (ADDR 03h, Default 43h)

#### **REG Offset Control**

The REG output (output of the step-up controller) voltage is set to the following value:

V<sub>REG</sub> default value is the maximum of either (V<sub>POS</sub> or -V<sub>NEG</sub>) + 300mV.

For example, if  $V_{POS} = 5.1V$  and  $V_{NEG} = -5V$ , then the default  $V_{REG} = 5.1V + 0.3V = 5.4V$

#### **Power Control**

ENP = Enable OUTP output.

ENN = Enable OUTN output.

EN Standby = Enable power on standby (the device is biased ON but the boost converter, the LDO, and the charge pump are OFF). Default is OFF for all 3 items.

Note: Turning ON either the OUTP or OUTN output will also turn-on the boost converter for the REG voltage.

#### **Fast Discharge**

Allows quick discharge of the OUTP and OUTN nodes when the outputs are disabled. Default is ON (1).

| Bit | t-7                                  | Bit-6                                                                                                                         | Bit-5 | Bit-4                                             | Bit-3                                             | Bit-2                                         | Bit-1                                            | Bit-0                                                       |

|-----|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------|---------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|

|     | 00<br>00<br>010 = 3<br>0<br>10<br>10 | fset Voltage<br>00 = 200mV<br>01 = 250mV<br>300mV (Defa<br>11 = 350mV<br>00 = 100mV<br>01 = 150mV<br>10 = 400mV<br>11 = 450mV |       | ENN Enable OUTN  0 = Disable (Default) 1 = Enable | ENP Enable OUTP  0 = Disable (Default) 1 = Enable | EN Standby  0 = Disable (Default)  1 = Enable | Discharge OUTP  0 = Disable 1 = Enable (Default) | Discharge<br>OUTN<br>0 = Disable<br>1 = Enable<br>(Default) |

#### **Capacitor Selection**

Small size X5R or X7R ceramic capacitors are recommended for the KTZ8812 application. 10µF capacitors are suggested for the input VIN, and for the outputs REG, OUTP, OUTN. The input capacitor should be placed as close as possible to the input pin and the PGND pin of the KTZ8812. For better input voltage filtering, this value can be increased. For the output capacitors, higher capacitor values can be used to improve the load transient response.

The capacitor data sheet determines what value of capacitor is required to guarantee a minimum capacitance value for a given bias voltage and over operating temperature.

| Capacitor | Comments              |  |  |

|-----------|-----------------------|--|--|

| 4.7μF/16V | C <sub>FLY</sub>      |  |  |

| 10µF/16V  | CIN, CPOS, CNEG, CREG |  |  |

| Manufacturer | Website         |

|--------------|-----------------|

| Murata       | www.murata.com  |

| AVX          | www.avx.com     |

| Taiyo Yuden  | www.t-yuden.com |

#### **Inductor Selection**

An inductor in the range of  $2.2\mu H$  to  $10\mu H$  with low DCR can be selected for the boost converter. To estimate the inductance required for applications, calculate the maximum input average current as the following

$$I_{\mathit{IN(MAX)}} = \frac{V_{\mathit{OUT}} \cdot I_{\mathit{OUT(MAX)}}}{V_{\mathit{IN}} \cdot \eta}$$

where  $\eta$  is the converter efficiency and can be approximated as 90% for the typical case. In order to have smaller current ripple (to improve efficiency and minimize output voltage ripple), larger inductance will be required. If inductor ripple current needs to be less than 40% of the average input current, then

$$\Delta I_L = \frac{V_{IN} \cdot D \cdot T_S}{L} \le 40\% \cdot \frac{V_{OUT} \cdot I_{OUT(MAX)}}{V_{IN} \cdot \eta}$$

Where duty cycle can be estimated as

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

Then

$$\Delta I_{L} = \frac{V_{IN} \cdot (V_{OUT} - V_{IN}) \cdot T_{S}}{L \cdot V_{OUT}} \le 40\% \cdot \frac{V_{OUT} \cdot I_{OUT(MAX)}}{V_{IN} \cdot \eta}$$

Therefore the inductance can be calculated as

$$L \ge \frac{V_{IN}^2 \cdot (V_{OUT} - V_{IN}) \cdot \eta}{40\% \cdot V_{OUT}^2 \cdot I_{OUT(MAX)} \cdot f_S}$$

where  $f_{\text{S}}$  is the switching frequency of the boost converter.

| Inductor Part Number | Value<br>(µH) | DCR (Ω)   | Saturation<br>Current (A) | Dimensions (mm) | Manufacturer |

|----------------------|---------------|-----------|---------------------------|-----------------|--------------|

| LPS3015-472ML        | 4.7           | 0.20 max  | 1.3                       | 3 × 3 × 1.5     | Coilcraft    |

| LPS3015-222ML        | 2.2           | 0.11 max  | 2.0                       | 3 × 3 × 1.5     | Coilcraft    |

| MIPS2520D2R2         | 2.0           | 0.11 typ. | 1.1                       | 2.5 x 2 x 1     | FDK          |

#### **CSP PC Board Layout**

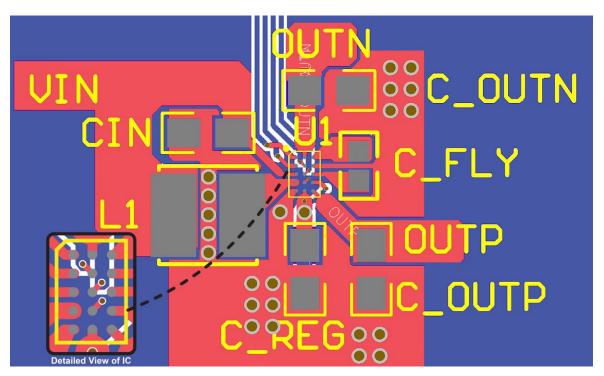

PCB layout is very important for high frequency switching regulators in order to keep the loop stable and minimize noise. A small 10µF ceramic capacitor CIN is recommended to be placed close to the IC VIN pin (C1) to get the best decoupling. The boost output capacitor CREG should located close the REG pin (E2) and with a direct contact to PGND pin (E1). The two REG pins must be tied together. The output (OUTP, OUTN) capacitors should also be located close to their respective pins (A2, E3). To minimize switching loss and EMI noise, the inductor L1 must adjacent to the SW pin (D1), and the charge pump capacitor C\_FLY should be next to the CFLY1/CFLY2 pins. The AGND pin (D2) is connected to the GND plane underneath using a micro via. The power GND plane should be uninterrupted, if possible. The I2C lines, SDA and SCL, are routed using micro vias. The KTZ8812 CSP recommended layout is shown in Figure 7.

Figure 7. CSP Recommended PCB Layout

# **Packaging Information**

#### WLCSP-15

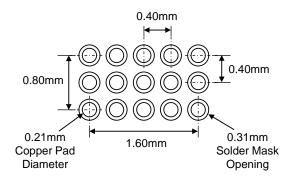

# **Recommended Footprint**

#### (NSMD Pad Type)

\* Dimensions are in millimeters.

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.